# **SPC Specification**

Version 1.0 Technical Report ARL-98-01 Janurary 8, 1998

> by: William Eatherton Toshiya Aramaki

Applied Research Laboratory Washington University

# DRAFT

# **1 INTRODUCTION**

- 2 Requirements of Target Applications

- **3** SPC Architecture

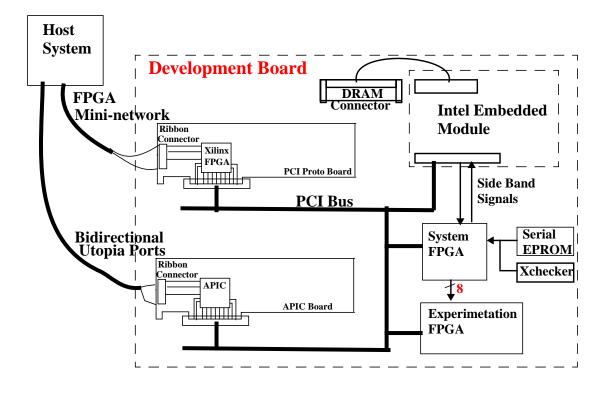

## 3.1 Overview

1. At power up or after a hard reset, the signal PWROK transitions (via analog reset circuitry) from deasserted to asserted. The PWROK signal enters the System FPGA chip. Initially the System FPGA outputs are all tristated (the reset lines it drives will be pulled down). When the board powers up, the FPGA will download its design from a serial eprom and then "turn on" its pads. When the PWROK signal is

RAFT

3

detected as asserted the system FPGA will with appropriate timing deassert the CPU and PCI reset signals.

- 2. Pentium does internal initialization and then does a memory read from address 0xfffffff0. At reset, the North Bridge chip has this memory area marked as disabled so read is passed to PCI bus.

- 3. The system FPGA will have this address hardwired as a decode to its embedded BIOS ROM. The first word of the bios is read out onto the PCI bus and passed to the CPU.

- 4. The CPU executes this instruction, which is usually a jump to the top half of the normal BIOS memory space 0xffff0000 (since we are 16 bytes from the end of memory).

- 5. The only POST check the BIOS will do is a memory check, where each physical memory address is written and read. When done, the results of the test will be written into a register of the FPGA.

- 6. The BIOS code at this point has the CPU do a simple 1000 iteration loop within an infinite loop that exits when a register in the System FPGA equals a non zero value(which is inited to zero at power up).

- 7. At some point the appropriate control processor (CP) which knows the control VCI of the APIC on the SPC under discussion, will start sending said APIC control cells.

- 8. First the CP processor has the APIC fetch the memory POST test results from the FPGA and send it back. If the test failed the CP processor halts OS loading.

- 9. Next the CP sets up the global APIC registers via control cells.

- 10. Then the CP has the APIC write a Rx descriptor starting a location 0x00000000. It describes an AAL5 packet splitting receive buffer 64Kbyes long at some set location in memory. Then descriptors are written for additional 64K buffers that will adequately hold the kernel. Finally, the CP resumes the connection and the APIC fetches the first descriptor

- 11. The CP then sends the first 64KB of the NetBSD OS as an AAL5 frame, when the RX buffer is full the APIC fetches the next descriptor until the entire OS (new boot loader code, kernel, and application) has been loaded into one contiguous block of memory. The remote control processor then reads all the returned descriptors and checks that the CRC values are correct.

- 12. At this point the DONE register in the system FPGA will be set to a non-zero value, and the next time the CPU checks the register it will jump out of its loop to the beginning of the OS code which will be the "newbootloader".

- 13.. the "newbootloader" does several BIOS emulation tasks: it writes a few parameters to the BIOS data area (Memory size, the time and date from the RTC), inits the interrupt table, enables the APIC and writes its base address for

slave access.

- 14. One the BIOS emulation tasks of the "newbootloader" is done, it executes the kernel (passing in the boot flags [i.e. single user boot, etc.]).

- 15. the kernel inits memory management, then inits devices. The kernel does not use any BIOS functions, but does access the BIOS data area left by the emulated bios.

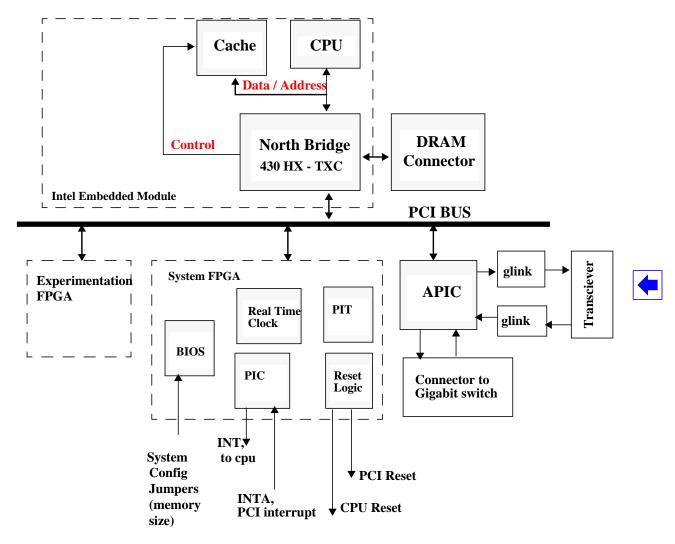

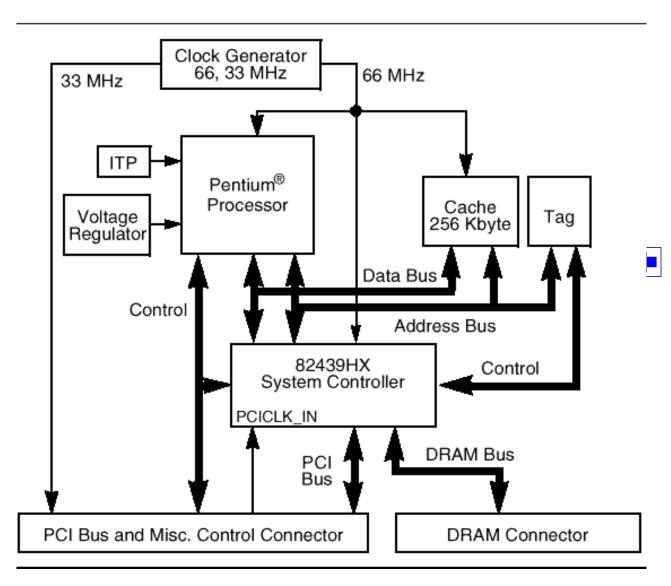

## 3.2 Intel Embedded Module

## 3.3 System FPGA

#### 3.3.1 Overview

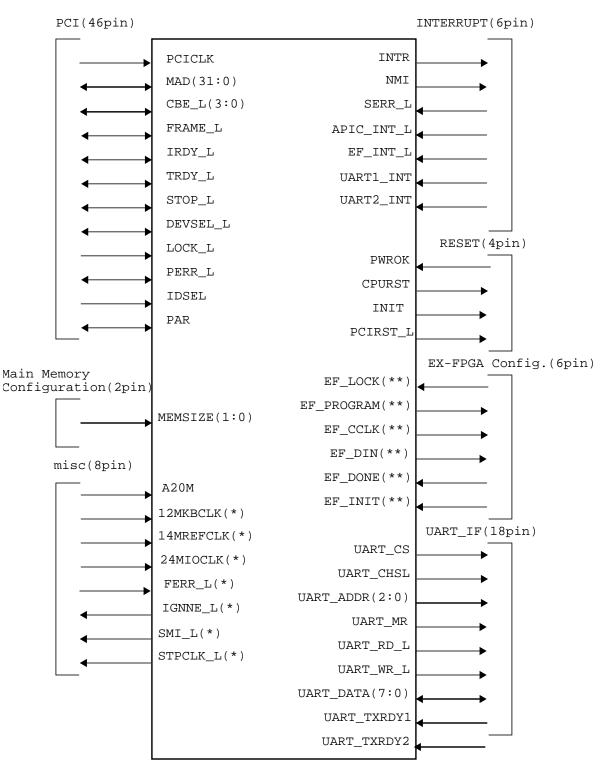

## 3.3.2 External Interface

(\*):These pins are assined but they are always disable.

$(\ensuremath{\,^{\star\star}})\xspace$  ):These pins are assined but any functions are not implimented .

RAF

DRAFT

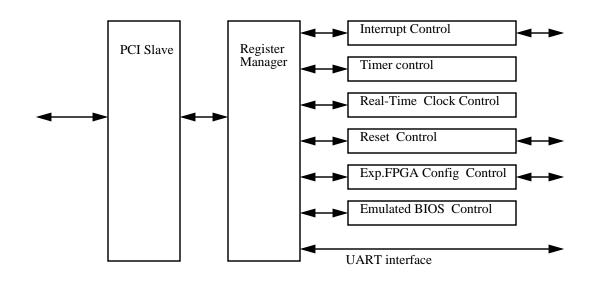

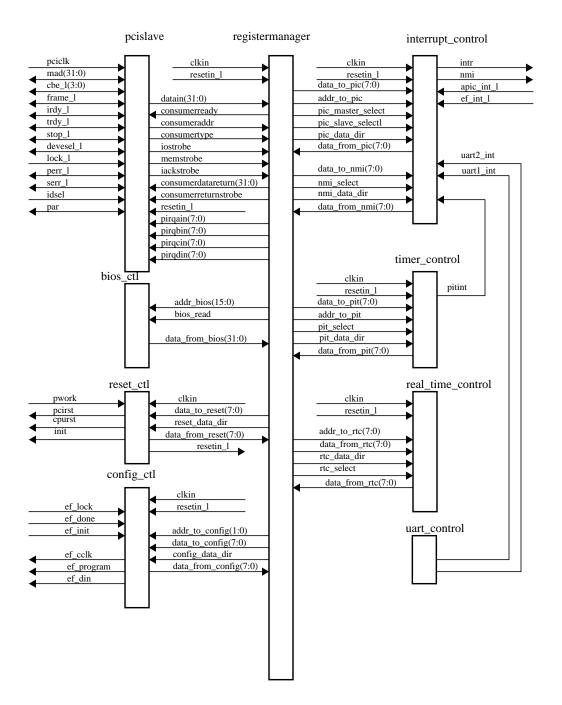

## 3.3.3 Block Diagram

#### 3.3.4 Pin Descriptions

| Signal             | Count                                          | Direction | Description                      |  |  |

|--------------------|------------------------------------------------|-----------|----------------------------------|--|--|

| PCI Interface Sign | PCI Interface Signals for both PCI32 and PCI64 |           |                                  |  |  |

| PCICLK             | 1                                              | Ι         | PCI Cock Input (0-33 Mhz)        |  |  |

| MAD(31:0)          | 32                                             | I/O       | Multiplexed Address/Data Bus     |  |  |

| CBE_L(3:0)         | 4                                              | I/O       | Command / Byte Enables           |  |  |

| FRAME_L            | 1                                              | I/O       | Cycle Frame                      |  |  |

| IRDY_L             | 1                                              | I/O       | Initiator Ready                  |  |  |

| TRDY_L             | 1                                              | I/O       | Target Ready                     |  |  |

| STOP_L             | 1                                              | I/O       | Stop indicator                   |  |  |

| DEVSEL_L           | 1                                              | I/O       | Device Select                    |  |  |

| LOCK_L             | 1                                              | Ι         | Bus Lock                         |  |  |

| PERR_L             | 1                                              | I/O       | Parity Error                     |  |  |

| IDSEL_L            | 1                                              | Ι         | Select for Config Space Accesses |  |  |

| PAR                | 1                                              | I/O       | Parity over PCI32                |  |  |

| Interrupt          |                                                |           |                                  |  |  |

| INTR10CPU InterruptNMI10Non Maskable InterruptSERR_L11PCI System errorAPIC_INT_L11PCI Interrupt from APICEF_INT_L10PCI Interrupt from Experimental FPGAUAR1_INT1IUARTI(COM1) interruptUAR1_INT1IUARTI(COM1) interruptRESETI0CPU RSTPWROK1IPower OKCPURST_L10PCI RSTPCIRST_L10PCI RSTPCIRST_L10PCI RSTPTIST_L10PCI RSTPCIRST_L10PCI RSTPCIRST_L10Experimental on Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FCA Configuration (Pin Experimental FPGA configuration dataClockEF_DIN10Experimental FPGA configuration dataEF_CCLK1IExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration stausEF_INIT1IExperimental FP                                         | Signal           | Count       | Direction      | Description                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|----------------|------------------------------------------------------|

| SERR_L1IPCI System errorAPIC_INT_L1IPCI Interrupt from APICEF_INT_L10PCI Interrupt from Experimental FPGAUAR1_INT1IUART1(COM1) interruptUAR1_INT1IUART1(COM1) interruptRESETI0CPU RSTPWROK1IPower OKCPURST10CPU RSTPCIRST_L10PCI RSTINIT10PCI RSTINIT10PCI RSTPEFOR10Experimental FPGA configuration is put off.)EF_DIN10Experimental FPGA configuration dataEF_CLK10Experimental FPGA configuration dataEF_PROGRAM10Experimental FPGA configuration dataEF_DIN11Experimental FPGA configuration dataEF_DONE11Experimental FPGA configuration dataEF_DONE11Experimental FPGA configuration statusEF_INIT11Experimental FPGA configuration statusEF_INIT11Experimental FPGA configuration statusEF_INIT10Chip Select.UART_CS10Chip Select.UART_CHSL10Chip Select.UART_ADDR20Register SelectUART_ADDR10Master ResetUART_RD_L10Master read                                                                                                                                                                             | INTR             | 1           | 0              | CPU Interrupt                                        |

| APIC_INT_L1IPCI Interrupt from APICEF_INT_L10PCI Interrupt from Experimental FPGAUAR1_INT1IUART1(COM1) interruptUAR1_INT1IUART1(COM1) interruptRESETI0CPU RSTPWROK1IPower OKCPURST10PCI RSTPIRST_L10PCI RSTINIT10PCI RSTINIT10PCI RSTINIT10Experimental FPGA configuration dataEF_DIN10Experimental FPGA configuration dataEF_CLK10Experimental FPGA configuration dataEF_CCLK10Experimental FPGA configuration dataEF_DONE1IExperimental FPGA configuration dataEF_DONE1IExperimental FPGA configuration dataEF_DONE1IExperimental FPGA configuration dataEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration data clockEF_ONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration status                                                              | NMI              | 1           | 0              | Non Maskable Interrupt                               |

| EF_INT_L10PCI Interrupt from Experimental FPGAUAR1_INT1IUART1(COM1) interruptUAR1_INT1IUART1(COM1) interruptRESETIIUART1(COM1) interruptPWROK1IPower OKCPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OExperimental configuration of function is put off.)EF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration dataEF_CCLK1IExperimental FPGA configuration dataEF_CCLK1IExperimental FPGA configuration dataEF_DONE1IExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_LOCK1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration data clockMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_ADDR1OMaster ResetUART_RD_L1OWART register read <td>SERR_L</td> <td>1</td> <td>Ι</td> <td>PCI System error</td> | SERR_L           | 1           | Ι              | PCI System error                                     |

| UAR1_INTIIUART1(COM1) interruptUAR1_INT1IUART1(COM1) interruptRESETPWROK1IPower OKCPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OExperimentation. Unlike a CPURST, the caches, write buffer, model registers and aloating-point register in Pentium are not reset.Experimentation-FVGA Configuration (Pin exceded sector)EF_DOIN1CPURST1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration dataEF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChannel SelectUART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_ADDR1OMaster ResetUART_RD_L1OUART register read                                                  | APIC_INT_L       | 1           | Ι              | PCI Interrupt from APIC                              |

| LARL_DYIIDefection and primeUAR I_INT1IUART1(COM1) interruptRESETPWROK1IPower OKCPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OExperimentation. Unlike a CPURST, the caches, write<br>in Pentium are not reset.Experimentation-FFGA Configuration (Pin assign only. Implimentation of function is put off.)EF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ComparityIIExperimental FPGA configuration error statusMain Memory ComparityIIIUART_CS1OChip Select.UART_CHSL1OChip SelectUART_ADDR2ORegister SelectUART_ADDR1OWaster ResetUART_RD_L1OUART register read                                                                                                                                     | EF_INT_L         | 1           | 0              | PCI Interrupt from Experimental FPGA                 |

| RESETPWROK1IPower OKCPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OInitialization. Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FPGA Configuration (Pin assign only. Implimentation of function is put off.)EF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DNE1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CSL1OChip SelectUART_ADDR2ORegister SelectUART_MR1OUART register read                                                                                                                                                                                        | UAR1_INT         | 1           | Ι              | UART1(COM1) interrupt                                |

| PWROKIIPower OKCPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OInitialization. Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FVFA Configuration (Proceed and Configuration of function is put off.)EF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration data clockEF_PROGRAM1IExperimental FPGA configuration data clockEF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusEF_INIT1IExperimental FPGA configuration error statusEF_INIT1IExperimental FPGA configuration error statusEF_INIT1IExperimental FPGA configuration error statusEF_INIT1IIMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OUART register read            | UAR1_INT         | 1           | Ι              | UART1(COM1) interrupt                                |

| CPURST1OCPU RSTPCIRST_L1OPCI RSTINIT1OPCI RSTINIT1OInitialization. Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FFGA Configuration (Pin exister)Experimental FPGA configuration dataEF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration dataEF_CCLK1IExperimental FPGA configuration dataEF_DROGRAM1OExperimental FPGA configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DNE1IExperimental FPGA configuration statusEF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChannel Select.UART_CMS1OChannel Select.UART_ADDR2ORegister Select.UART_MR1OWaster ResetUART_RD_L1OWaster read                                                                                                                                                            | RESET            | ·           |                |                                                      |

| PCIRST_L10PCI RSTINIT10PCI RSTINIT10Initialization. Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FPGA Configuration (Pin assign only. Implimentation of function is put off.)EF_DIN10EF_CCLK10EF_PROGRAM10EF_LOCK1IEF_LOCK1IEF_DONE1IEF_DONE1IIEF_DONE1IIEF_DONE1IIEF_INIT1IIEF_CCLKIIIIEF_DONEIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII <td>PWROK</td> <td>1</td> <td>Ι</td> <td>Power OK</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PWROK            | 1           | Ι              | Power OK                                             |

| INIT1OInitialization. Unlike a CPURST, the caches, write<br>buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation-FPGA Configuration (Pin are not reset.Experimental FPGA configuration dataEF_DIN1OExperimental FPGA configuration dataEF_CCLK1OExperimental FPGA configuration data clockEF_PROGRAM1IExperimental FPGA configuration data clockEF_LOCK1IExperimental FPGA configuration data clockEF_DNE1IExperimental FPGA configuration data clockEF_DNE1IExperimental FPGA configuration data clockEF_INIT1IExperimental FPGA configuration data clockMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB,<br>10=64MB, 11=128MB.UART_CS1OChip Select.UART_CS1OChip Select.UART_ADDR2ORegister SelectUART_ADDR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                     | CPURST           | 1           | 0              | CPU RST                                              |

| buffer, model registers and aloating-point register<br>in Pentium are not reset.Experimentation of function is put off.)EF_DIN1OExperimental FPGA configuration dataEF_CLK1OExperimental FPGA internal configuration dataEF_PROGRAM1OExperimental FPGA internal configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMemory CorrectorIIIMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB,<br>10=64MB, 11=128MB.UART_CS1OChip Select.UART_CS1OChip Select.UART_ADDR2ORegister SelectUART_ADDR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                        | PCIRST_L         | 1           | 0              | PCI RST                                              |

| EF_DIN10Experimental FPGA configuration dataEF_DIN10Experimental FPGA configuration dataEF_CCLK10Experimental FPGA configuration data clockEF_PROGRAM10Experimental FPGA internal configuration dataEF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationIIExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChip SelectUART_ADDR20Register SelectUART_MR1OUART register read                                                                                                                                                                                                                                                                                                                                                                | INIT             | 1           | 0              | buffer, model registers and aloating-point register  |

| EF_CCLK1OExperimental FPGA configuration data clockEF_PROGRAM1OExperimental FPGA internal configuration data<br>reset.EF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration data clockEF_INIT1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationIIExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB,<br>10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                 | Experimentation- | FPGA Config | uration (Pin a | assign only. Implimentation of function is put off.) |

| EF_PROGRAM1OExperimental FPGA internal configuration data<br>reset.EF_LOCK1IExperimental FPGA configuration data clockEF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationIExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EF_DIN           | 1           | 0              | Experimental FPGA configuration data                 |

| EF_LOCK1IExperimental FPGA configuration data clockEF_LOCK1IExperimental FPGA configuration statusEF_DONE1IExperimental FPGA configuration error statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationIExperimental FPGA configuration error statusMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EF_CCLK          | 1           | 0              | Experimental FPGA configuration data clock           |

| EF_DONE1IExperimental FPGA configuration statusEF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.MEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART_CS1OChip Select.UART_CS1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EF_PROGRAM       | 1           | 0              |                                                      |

| EF_INIT1IExperimental FPGA configuration error statusMain Memory ConfigurationMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART interfaceUART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EF_LOCK          | 1           | Ι              | Experimental FPGA configuration data clock           |

| Main Memory ConfigurationMEMSIZE2IMain Memory Size. 00=16MB, 01=32MB, 10=64MB, 11=128MB.UART interfaceUART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EF_DONE          | 1           | Ι              | Experimental FPGA configuration status               |

| MEMSIZE2IMain Memory Size. 00=16MB, 01=32MB,<br>10=64MB, 11=128MB.UART interfaceUART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EF_INIT          | 1           | Ι              | Experimental FPGA configuration error status         |

| UART interfaceUART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Main Memory Co   | nfiguration | •              |                                                      |

| UART_CS1OChip Select.UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MEMSIZE          | 2           | I              | •                                                    |

| UART_CHSL1OChannel SelectUART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UART interface   | ·           | ·              |                                                      |

| UART_ADDR2ORegister SelectUART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UART_CS          | 1           | 0              | Chip Select.                                         |

| UART_MR1OMaster ResetUART_RD_L1OUART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UART_CHSL        | 1           | 0              | Channel Select                                       |

| UART_RD_L 1 O UART register read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UART_ADDR        | 2           | 0              | Register Select                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UART_MR          | 1           | 0              | Master Reset                                         |

| UART_WR_L 1 O UART register write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UART_RD_L        | 1           | 0              | UART register read                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UART_WR_L        | 1           | 0              | UART register write                                  |

Table 1:

DRAFT

| Signal    | Count | Direction | Description                                                                                                   |

|-----------|-------|-----------|---------------------------------------------------------------------------------------------------------------|

| UART_DATA | 8     | I/O       | Data to/from UART                                                                                             |

|           |       |           |                                                                                                               |

| Misc      |       |           |                                                                                                               |

| A20M      | 1     | I         | Address Bit 20 Mask. When enabled, this causes<br>the processor to emulate the address wraaparound<br>at 1MB. |

| 12MKBCLK  | 1     | I         | 12MHz Clock. This clock is not used in the Sytem FPGA.                                                        |

| 14MREFCLK | 1     | I         | 14.318MHz Clock. This clock is not used in the Sytem FPGA.                                                    |

| 24MIOCLK  | 1     | I         | 24MHz Clock. This clock is not used in the Sytem FPGA.                                                        |

| FERR_L    | 1     | I         | Numeric Coprocessor Error. This signal is not used in the Sysytem FPGA                                        |

| IGNNE_L   | 1     | 0         | Ignore Error. Always disable.                                                                                 |

| SMI_L     | 1     | 0         | System Management Interrupt. Always disable.                                                                  |

| STPCLK_L  | 1     | 0         | Stop Clock. Always disable.                                                                                   |

|           |       |           |                                                                                                               |

|           |       |           |                                                                                                               |

Table 1:

#### 3.3.5 Register Overview

Table2, Table3 show the I/O assignments for PCI Configuration Registers and System Resource Registers. I/O register address to access System Resources in this FPGA is compatible with Intel PIIX3(82371FB).

| Configuration<br>Offset | Register              | Access |

|-------------------------|-----------------------|--------|

| PCI Device Independen   | t Region              |        |

| 00-01h                  | Vendor Identification | RO     |

| 02-03h                  | Device Identification | RO     |

| 04-05h                  | PCI Command           | R/W    |

| 06-07h                  | PCI Status            | R/WC   |

| Configuration<br>Offset       | Register                         | Access |  |

|-------------------------------|----------------------------------|--------|--|

| 08h                           | Revision ID                      | RO     |  |

| 09-0Bh                        | Class Code                       | RO     |  |

| PCI Device Header Type Region |                                  |        |  |

| 10h                           | Base Address Register for Memory | R/W    |  |

| 14h                           | Base Address Register for I/O    | R/W    |  |

| SYSTEM FPGA dependent Region  |                                  |        |  |

| 60-63h                        | PCI IRQ[A:D] Route Control       | RO     |  |

## Table 2:

| Address                | Register                          | Access |  |  |

|------------------------|-----------------------------------|--------|--|--|

| System Resource Region | System Resource Region            |        |  |  |

| 0020h                  | INT1 Control                      | R/W    |  |  |

| 0021h                  | INT1 Mask                         | R/W    |  |  |

| 0040h                  | Timer Counter 1 - Counter 0 Count | R/W    |  |  |

| 0061h                  | NMI Status and Control            | R/W    |  |  |

| 0070h                  | CMOS RAM Address and NMI Mask Reg | WO     |  |  |

| 00A0h                  | INT2 Control                      | R/W    |  |  |

| 00A1h                  | INT2 Mask                         | R/W    |  |  |

| 04D0h                  | INT-1 edge/level control          | R/W    |  |  |

| 04D0h                  | INT-1 edge/level control          | R/W    |  |  |

| 0CF9h                  | Reset Control                     | R/W    |  |  |

| 0D00h                  | Exp. FPGA Configuration start     | R/W    |  |  |

| 0D04h                  | Exp. FPGA Configuration data      | WO     |  |  |

| 0D08h                  | Exp. FPGA Configuration status    | R/WC   |  |  |

Table 3:

DRAFT

| Address                                                | Memory | Access |

|--------------------------------------------------------|--------|--------|

| Emulated BIOS                                          |        |        |

| FFFE 0000h-FFFE<br>FFFFh<br>(000E 0000h-000E<br>FFFFh) | BIOS   | RO     |

Table 4:

## **3.4 APIC**

## 4 NetBSD and SPC

- 4.1 Overview

- 4.2 Boot Loader Code Modifications

- 4.3 Memory based Filesystem

## **5** System FPGA Register Descriptions

## 5.1 PCI Configuration register

#### 5.1.1 Vender Identification

| Address Offset: | 00h 01h   |

|-----------------|-----------|

| Default value:  | xxxxh     |

| Attribute:      | Read Only |

This register uniquely identifies any PCI device along with the Device Identification Register.

| Bit  | Description                                           |

|------|-------------------------------------------------------|

| 15:0 | Vendor Identification Number. This is a 16 bit-value. |

#### 5.1.2 Device Identification

| Address Offset: | 02h 03h   |

|-----------------|-----------|

| Default value:  | xxxxh     |

| Attribute:      | Read Only |

This register uniquely identifies any PCI device along with the Vendor Identification Register.

LE VU

DRAFT

| Bit  | Description                                                   |

|------|---------------------------------------------------------------|

| 15:0 | <b>Device Identification Number</b> . This is a 16 bit-value. |

#### Table 6:

## 5.1.3 Command Register

| Address Offset: | 04h 05h         |

|-----------------|-----------------|

| Default value:  | 0003h           |

| Attribute:      | Read/Write Bit[ |

This register provides basic control over the System FPGA to respond to PCI cycle.

| Bit   | Description                                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 | Reserved.                                                                                                                                             |

| 9     | <b>Fast back to back Enable</b> . This bit must be a 1 since the System FPGA does not have Fast Back to Back function.                                |

| 8     | <b>SERR Enable</b> . 1=SERR signal drive Enable, 0=SERR signal drive Disable.                                                                         |

| 7     | Wait Cycle Control. This bit must be 0. Read Only.                                                                                                    |

| 6     | Parity Error Response. 1=Enable, 0=dsiable.                                                                                                           |

| 5     | <b>VGA Palette Snoop</b> . This must be 0 since the System FPGA does not have VGA Palette Snooping function.                                          |

| 4     | <b>Memory Write and Invalidate Enable</b> . This bit must be 0 since the System FPGA does not have this function.                                     |

| 3     | <b>Special Cycle Enable</b> . 1=Enable, the System FPGA recognizes shutdown special cycle. 0=Disable, the System FPGA ignores all PCI Special Cycles. |

| 2     | <b>Bus Master Access Enable</b> . This bit is hardwired to 0 since the System FPGA does not have this function.                                       |

| 1     | <b>Memory Access Enable</b> . This bit hardwired to 1 since the System FPGA cans response to Memory space access.                                     |

| 0     | <b>I/O Space Access Enable</b> . This bit hardwired to 1 since the System FPGA can response to I/O Space Address.                                     |

Table 7:

## 5.1.4 PCI Device Status Register

| Address Offset: | 06h 07h                        |

|-----------------|--------------------------------|

| Default value:  | 0200h                          |

| Attribute:      | Read/Write Clear(by writing 1) |

| Bit  | Description                                                                                                                                                                                                                                                                                                              |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15   | <b>Detected Parity Error</b> . Status. 0=the System FPGA did not detect a parity error. 1=the System FPGA detected parity error.                                                                                                                                                                                         |  |

| 14   | <b>Detected Signaled System Error Status</b> . 0=the System FPGA did not generate a system error on the SERR line. 1=the System FPGA detected parity error generates a system error on the SERR line.                                                                                                                    |  |

| 13   | <b>Received Master Abort Status</b> . This bit must be 0 since the System FPGA does not have the bus master function.                                                                                                                                                                                                    |  |

| 12   | <b>Received Target Abort Status</b> . This bit must be 0 since the System FPGA does not have the bus master function.                                                                                                                                                                                                    |  |

| 11   | <b>Signaled Target Abort Status</b> . This bit is set when the System FPGA is targeted with a transaction that the System FPGA terminates with a target abort. Writing a 1 clear this bit.                                                                                                                               |  |

| 10:9 | Device Select Timing Status. The System FPGA always generates DEVSEL with<br>slow(??) timing. These bits are read only.<br>bits[10:9]bits[10:9]Functions00The System FPGA asserts DESEL in the fast mode.01The System FPGA asserts DESEL in the medium mode.10The System FPGA asserts DESEL in the slow mode.11reserved. |  |

| 8    | <b>Device Parity Status</b> . This bit must be 0 since the System FPGA does not support the bus master function. Writing a 1 clear this bit.                                                                                                                                                                             |  |

| 7    | <b>Fast Back to Back</b> . This bit must be 0 since the System FPGA does not support this function.                                                                                                                                                                                                                      |  |

| 6:0  | Reserved. Read as 0s                                                                                                                                                                                                                                                                                                     |  |

Table 8:

## 5.1.5 Revision Identification

| Address Offset: | 08h       |

|-----------------|-----------|

| Default value:  | xxxxh     |

| Attribute:      | Read Only |

This register contains device stepping information.

| Bit  | Description                                          |

|------|------------------------------------------------------|

| 15:0 | Revision ID Byte. These bits are hardwired to xxxxh. |

Table 9:

#### 5.1.6 Class Code

| Address Offset: | 0Bh     |

|-----------------|---------|

| Default value:  | 060100h |

Attribute:

Read Only

This register indicates the device programming interface information related to the Sub-Class Code and Base Class Code definition fro the System FPGA. This register also identifies the Base Class Code and the function sub class in relation to the Base Class Code.

| Bit   | Description                                                  |

|-------|--------------------------------------------------------------|

| 23:16 | Base Class Code (BASEC). 06h=Bridge device.                  |

| 15:8  | Sub-Class Code(SCC). 01h= PCI-to-ISA Bridge.                 |

| 7:0   | Programming Interface. 00h=hardwired as a PCI-to-ISA Bridge. |

| Table | 10: |

|-------|-----|

|-------|-----|

#### 5.1.7 PIRQ[A:D] Route Control Register

Address Offset: PIRQRCA#-060h -- PIRQRCD#-063h

This resister is in PCI configuration Registers space.

Default value: PIRQRCA:80h, PIRQRC[B:D]:00h

Attribute: Read Only

These registers control the routing of the PIRQ[A:D] signals to the IRQ inputs of the interrupt controller. In the Sysytem FPGA, Interrupt Routing bits in these registers are hardwired. When a PIRQ signal is routed to an interrupt controller IRQ, the System FPGA can mask the corresponding IRQ signal.

| Bit | Description                                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | <b>Interrupt Routing Enable</b> . 1=Disable; 0=Enable. In PIRQRC[B:D], this bit is hard-<br>wired to 1 because PIRQ[B:D] are not used in SPC. In PIRQRCA, this bit is hardwired<br>to 0. |

| 6:4 | Reserved. These bit are hardwired to 0s.                                                                                                                                                 |

| 3:0 | Interrupt Routing.<br>In PIRQRCA, these bits are hardwired to 0101b to connect to IRQ5. In other registers, these bits are hardwired to 0000b.                                           |

#### Table 11:

## 5.2 System Resource Register

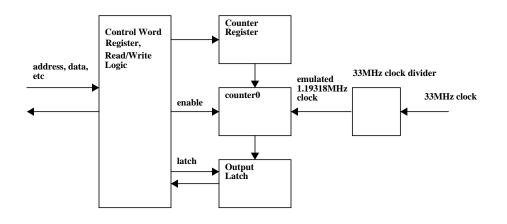

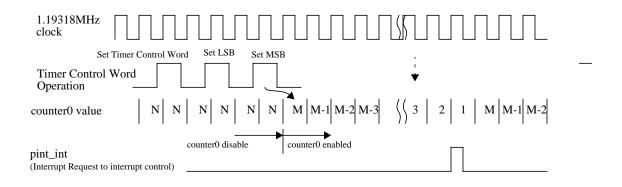

#### 5.2.1 Timer/Counter Registers

The System FPGA contains the functionality of 8254 Programmable Interval Timer(PIT) like a Intel PIIX3. The registers are compatible with the registers in PIIX3. The interrupt registers control the operation of PIT. However, some functions which are not essential to SPC are deleted from the original 8254.

#### 5.2.1.1. TCW: Timer Control Word Register

I/O Address: 043h

Default value:bit[7:6]=00b, bit[5:4]=undefined, bit[3:0]=0101bAttribute:Write Only

The Timer Control Word Register specifies the counter selection, the operating mode, the counter byte programming order and size of count value, and whether the counter counts down in a 16-bit or BCD format. After writing the control word, anew count can be written at any time. The new value takes effect according to the programmed mode.

| Bit | Description                                                                                                                                                                                                                            |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6 | Counter select. If a timer is selected, bits[7:6] are be both 0 since the System FPGAhas a timer0 only. The read back Command is selected when bit s[7:6] are both 1. Writing other values are ignored.Bit[7:6]Function00Timer0 select |  |

| 5:4 | Read/Write select.Bit[5:4]Function00Counter Latch Command01R/W Least Significant Byte10R/W Most Significant Byte11R/W LSB then MSB                                                                                                     |  |

| 3:1 | <b>Counter Mode Select</b> . The System FPGA supports Rate Generator mode only. These bits is hardwired to 010b. Writing other value is ignored.                                                                                       |  |

| 0   | <b>Binary/BCD Countdown Select</b> . The Stem FPGA supports binary countdown mode only. This bit is hardwired to 1. The largest possible binary count is 2**16.                                                                        |  |

#### **Table 12:**

#### **Counter Latch Command**

The Counter Latch Command latches the current count value at the time the command is received. If a counter is latched once and then, come time later, latched again before the count is read, the second Counter latch Command is ignored. If the counter is programmed for two byte counts, two bytes must be read. The two bytes do not have to be read successively.

| Bit | Description                                                                                                                                                                                                                                                             |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6 | Counter Latch Command.Bit[7:6]Function00latch counter 0 select11Read Back CommandThese bits must be set to 00 to select the Counter Latch Command. Other values areignored since the System FPGA does not support other counters.                                       |  |

| 5:4 | <b>Counter Latch Command</b> . When bits[5:4] = 00, the Counter Latch Command is selected during a write to the Timer Control Word Register. Following the Counter Latch Command, I/O read from the selected counter's I/O addresses produce the current latched count. |  |

#### 5.2.1.2. Counter Access Port Register

| I/O Address:   | Counter 0 040h    |

|----------------|-------------------|

| Default value: | All bit undefined |

| Attribute:     | Read/Write        |

This register is used for writing count values to the Count Registers; reading the current count value from the counter by either an I/O read, after a counter-latch command.

| Bit | Description                                                                                                                                                                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | <b>Counter Port bit</b> . These bits are used to program the 16bit Count Register. The order of programming, either LSB only, or LSB then MSB, is defined with the interval Counter Control Register. The counter I/O port is also used to read the current count from the Count Register. |

**Table 14:**

#### 5.2.2 Interrupt Controller Registers

The System FPGA contains the functionality of two 82C59 interrupt controllers like a Intel PIIX3. The registers are compatible with the registers in PIIX3. The interrupt registers control the operation of the interrupt controller. However, some functions which are not essential to SPC are deleted from the original 82C59.

#### 5.2.2.1. ICW1: Initialization Command Wor1 Register

| I/O Address:   | INT CTRL-1020h; INT CTRL-10A0h |

|----------------|--------------------------------|

| Default value: | 11h                            |

| Attribute:     | Write Only                     |

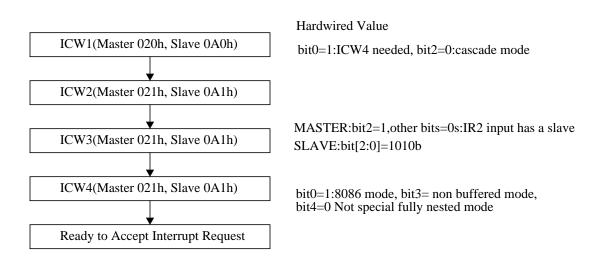

A write to Initialization Command Word 1 starts the interrupt controller initialization sequence. An I/O write to the CTRL-1 or CTRL-2 base address (020h or 0A0h) with bit 4 in data equal to 1 is interpreted as ICW1. The interrupt controller initialization must follow sequence described in Fig X.

ICW1 starts the initialization sequence during which the following automatically occur;

16.The Interrupt Mask register is cleared.

17.IRQ7 input is assigned priority7.

18. The slave mode address is set to 7.

19.Special Mask Mode is cleared and Status Read is set to IRR

20.If IC4(see bellow) was set to 0, then all functions selected by ICW4 are set to 0.

| Bit | Description                                                                                                                                                                                                               |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | ICW/OCW select. Theses bits should be 000 to select ICW1.                                                                                                                                                                 |

| 4   | <b>ICW/OCW select</b> . Bit 4 must be a 1 to select ICW1. A 1 on this bit at any time will force the interrupt controller to interpret the write as an ICW1. The controller will then expect to see ICW2, ICW3, and ICW4. |

| 3   | <b>Edge/Level Bank Select (LTIM)</b> . This bit is ignored. Its function is replaced by the Edge/Level Triggered Control (ELCR) Registers.                                                                                |

| 2   | ADI. Ignored for the System-FPGA.                                                                                                                                                                                         |

| 1   | Single of Cascade(SNGL). This bit is hardwired to a 0(cascade).                                                                                                                                                           |

| 0   | ICW4 Write Required(IC4). This bit is hardwired to a 1(ICW4 is required).                                                                                                                                                 |

#### Table 15:

#### 5.2.2.2. ICW3:Initialization Command Wor2 Register

| I/O Address:   | INT CTRL-1021h; INT CTRL-10A1h        |

|----------------|---------------------------------------|

| Default value: | bits[7:3]= undefined, bits[2:0]=000b. |

| Attribute:     | Write Only                            |

Initialization Command Word 2 is used to initialize the interrupt controller with the time most significant bits of the interrupt vector address.

| Bit | Description                                                                                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | <b>Interrupt Vector Base Address</b> . Bit[7:3] define the base address in the interrupt vector table for the interrupt routines associated with each interrupt request level input. |

| 2:0 | Interrupt Request Level. These bits are hardwired to all 0s.                                                                                                                         |

#### Table 16:

#### 5.2.2.3. ICW3: Initialization Command Word3 Register for Master PIC

| I/O Address:   | INT CTRL-1021h |

|----------------|----------------|

| Default value: | 02h            |

| Attribute:     | Write Only     |

The meaning of ICW3 differs between CTRL-1(Master) and CTRL-2(Slave). On CTRL-1, ICW3 indicates which CTRL-1 IRQ line physically connects the INTR output of CTRL-2 to CTRL-1.

| Bit | Description                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved. These bits are hardwired to all 0s.                                                                                                              |

| 2   | <b>Cascade Mode Enable</b> . This bit is hardwire to 1 to select the cascade mode. This indicates IRQ2 of the master controller connects the slave's INTR. |

| 1:0 | Reserved. These bits are hardwired to all 0s.                                                                                                              |

#### 5.2.2.4. ICW3: Initialization Command Word3 Register for Slave PIC

| I/O Address:   | INT CTRL-20A1h     |

|----------------|--------------------|

| Default value: | All bits undefined |

| Attribute:     | 02h                |

#### On CTRL-2, ICW3 is the slave identification code broadcast by CTRL-1.

| Bit | Description                                                                                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved. These bits are hardwired to all 0s.                                                                                                |

| 2:0 | <b>Slave Identification Code</b> . These bits are hardwired to 010b. This indicates IRQ2 of the master controller connects the slave's INTR. |

#### 5.2.2.5. ICW4:Initialization Command Word4 Register

| I/O Address:   | INT CNTRL-1021h; CTRL-20A1h |

|----------------|-----------------------------|

| Default value: | 01h                         |

| Attribute:     | Write Only                  |

ICW4 must be programmed as part of their initialization sequence.

| Bit | Description                                         |

|-----|-----------------------------------------------------|

| 7:5 | <b>Reserved</b> . These bits must be set to all 0s. |

| _ |

|---|

|   |

|   |

|   |

|   |

| Bit | Description                                                                                                                                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | <b>Special Fully Nested Mode(SFNM)</b> . Bit4 is hardwired to 0. Special Fully Nested Mode is not supported by the System FPGA.                                                              |

| 3   | <b>Buffered mode</b> ( <b>BUF</b> ). This bit is hardwired to 0. Writing 1 on this bit is ignored.                                                                                           |

| 2   | Master/Slave in Buffered mode(BUF). This bit is hardwired to 0.                                                                                                                              |

| 1   | <b>AEOI</b> (Automatic End of Interrupt). This bit should normally be programmed to 0.<br>This is the normal end of interrupt. If this bit is 1, the automatic end of interrupt mode is set. |

| 0   | <b>Microprocessor Mode</b> . This bit is harwired to 1. A 1 on this bit indicate Intel 8086 architecture-based system.                                                                       |

Table 19:

#### 5.2.2.6. OCW1: Operational Control Wor1 Register

| I/O Address:   | INT CNTRL-1021h; CTRL-20A1h |

|----------------|-----------------------------|

| Default value: | OOh                         |

| Attribute:     | Read/Write                  |

OCW1 sets and clears the mask bits in the Interrupt Mask Register(IMR). The IMR operates on the IRR. Masking of a higher priority input does not affect the interrupt request of lower priority. For reading the IMR, OCW3 is not needed. The output bus contains the IMR when an I/O read is active and the I/O address is 021h or 0A1h. All writes to OCW1 must occur following the ICW1-ICW4 initialization sequence, since the same I/O ports are used for OCW1, ICW2, OCW3, and ICW4.

| Bit | Description                                                                                                                                                                                                                                                                                                                                                            |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | <b>Interrupt Request Mask (Mask[7:0]).</b> When a 1 is set on any bit in this register, the corresponding IRQx line is masked and do not set the Interrupt Request Register(IRR) When a 0 is set on any bit in this register, the corresponding IRQx line is unmasked. Masking IRQ2 on CTRL-1 also masks the interrupt request from CTRL-2, which is cascaded to IRQ2. |

#### **Table 20:**

#### 5.2.2.7. OCW2: Operational Control Wor2 Register

| I/O Address:   | INT CNTRL-1020h; CTRL-20A0h                        |

|----------------|----------------------------------------------------|

| Default value: | bits[7:5]=001b, bits[4:3]=undefined, bit[2:0]=000b |

| Attribute:     | Write Only                                         |

OCW2 controls the Rotate Mode and the End of Interrupt mode. Following a CPURST or ICW initialization, the controller enters the fully nested mode of operation. Both rotation mode and specific EOI mode are disabled following initialization.

| Bit | Description                                                                                                                                                                                                                  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:5 | Rotate and EOI codes.R,SL,EOI - These bits control the Rotate and EOI mode and<br>combinations of the two. The System FPGA supports the following mode only.Bits[7:5]Functions001:Non-specific EOI command                   |  |

| 4:3 | <b>OCW2 Select</b> . These bits must be set to 00 to select OCW2                                                                                                                                                             |  |

| 2:0 | <b>Interrupt Level Select(L2,L1,L0)</b> . L2, L1, and L0 determine the interrupt level acted upon when SL bit(bit 6) is active. In the System FPGA, the SL bit is hardwired to non active. Then, L2, L1, and L0 are ignored. |  |

**Table 21:**

#### 5.2.2.8. OCW3: Operational Control Wor3 Register

| I/O Address:   | INT CNTRL-1020h; CTRL-20A0h                        |

|----------------|----------------------------------------------------|

| Default value: | bit[7:5]=100b, bits[4:3]=undefined, bits[2:0]=010b |

| Attribute:     | Read/Write                                         |

OCW3 serves Enable Special Mask Mode, Poll Mode control, and IRR/ISR register read control.

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | <b>Reserved</b> . This bit is hardwired to 1.                                                                                                                                                                                                                                                                                                                                                                        |  |

| 6   | <b>Special Mask Mode(SMM)</b> . This bit is hardwired to 0. Special Mask Mode is always disabled.                                                                                                                                                                                                                                                                                                                    |  |

| 5   | <b>Enable Special Mask Mode(ESMM)</b> . This bit is hardwired to 0. This disables SMM bit.                                                                                                                                                                                                                                                                                                                           |  |

| 4:3 | OCW3 Select. These bits must be set to 01 to select OCW3                                                                                                                                                                                                                                                                                                                                                             |  |

| 2   | <b>Poll Mode Command</b> . 0= Disable Poll Mode Command. This bit is hardwired to 0.                                                                                                                                                                                                                                                                                                                                 |  |

| 1:0 | Register Read Command. Bits[1:0] provides control for reading the In-Service Register(ISR) and the interrupt Request Register(IRR). Following ICW initialization, the<br>default OCW3 port address read will be "read IRR". To retain the current selection,<br>always write a 0 to bit 1 when programming this register.Bits[2:0]Functions<br>00:00:No Action<br>10:10:Read IRR Register<br>11:11:Read ISR Register |  |

#### 5.2.3 NMI Register

The NMI logic incorporates two different 8-bit registers. The CPU reads the NMISC Register to determine the NMI source. In this SYSTEM-FPGA, the NMI source is only PCI SERR. After the NMI interrupt routine processes the interrupt, software clears the NMI status bit by setting the corresponding enable/disable bit to a 1. The NMI Enable and Real-Time Clock register can mask the NMI signal and disable/enable all NMI sources.

To ensure that all NMI requests are serviced, the NMI service routine software flow should be as follows,

1.NMI is detected by the processor on the rising edge of the NMI input.

2. The processor will read then set to the status stored in port 061h to determine what sources caused the NMI. The Processor may the set to 0 the register bits controlling the sources that it has determined to be active. Between the time the processor reads the NMI sources and sets them to a 0, an NMI may have been generated by another source. The level of NMI will then remain active. This new NMI source will not be recognized by the processor because there was no edge on NMI.

3. The processor must then disable all NMIs by setting bit 7 of port 070h to a 1 and then enable all NMIs by setting bit 7 of port 070h to a 0. This will cause the NMI output to transition low then high if there are any pending NMI sources. The CPU's NMI input logic will then register a new NMI.

#### 5.2.3.1. NMI Status And Control Register (NMISC)

| I/O Address:   | 061h       |

|----------------|------------|

| Default value: | 00h        |

| Attribute:     | Read/Write |

This register reports the status of PCI SERR status as a NMI source.

| Bit | Description                                                                                                                                                                                                                                                                             |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | <b>SERR# NMI Source Status</b> . Bit 7 is set if a PCI device detects a system board error and pulses the PCI SERR# line. This interrupt source is enabled by setting bit2 to 0. To reset the interrupt, set bit2 to 0 and then set it to 1. When writing to port 061h, bit7 must be 0. |  |

| 6:3 | <b>Reserved</b> . These bits are hardwired to 0s.                                                                                                                                                                                                                                       |  |

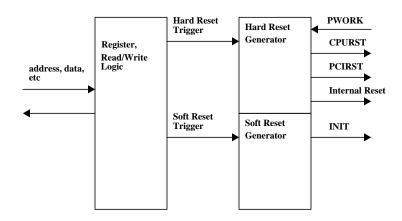

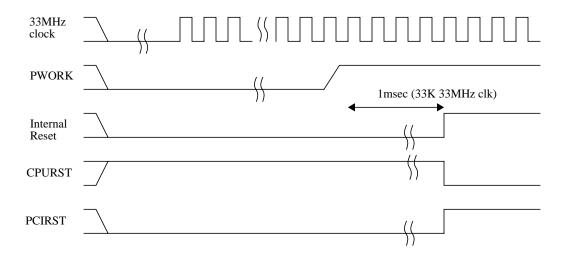

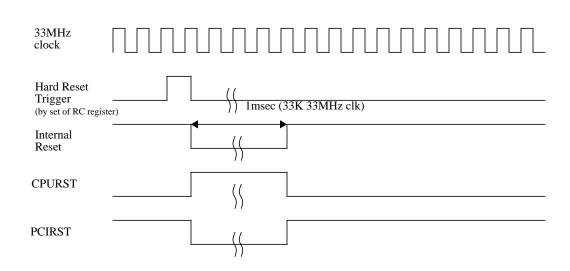

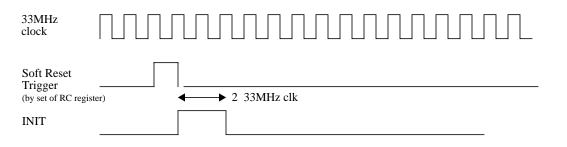

| 2   | <b>PCI SERR# Enable</b> . 1= Clear and Disable; 0= Enable.                                                                                                                                                                                                                              |  |