# ADVANCED COMMUNICATIONS SYSTEMS

Jonathan S. Turner (PI) September 1, 1986 - August 31, 1987 WUCS-87-22

Mark A. Franklin

Pierre Costa Riccardo Melen

Shahid Akhtar

Neil Barrett

Victor Griswold

Mark Hunter

Shabbir Khakoo

George Robbert

James Sterbenz

Bernard Waxman

Einir Valdimarssen

David Wexelblat

### Copy to:

Shahid Akhtar Akira Arutaki Neil Barrett Pierre Costa Jerome R. Cox, Jr. Maurizio Dècina — Italtel Mark A. Franklin Victor Griswold Neil Haller\* - Bellcore Joe Hui - Bellcore Mark Hunter Akihiro Kitamura\* - NEC Shabbir Khakoo Tony Lee - Bellcore Riccardo Melen Eric Nussbaum — Bellcore George Robbert Anna Robrock\* - Italtel J. Shimuzu - NEC Dave Sincoskie - Bellcore Barry Spielman James Sterbenz N. Suzuki – NEC Giuseppe Valbonesi – Italtel Einir Valdimarssen Bernard Waxman Ken Wong Liang Wu - Bellcore T. Yamaguchi - NEC

## Research Objectives

The Advanced Communications Systems Project is concerned with new communications technologies that can support a wide range of different communications applications in the context of of large public networks. Communications networks in common use today have been tailored to specific applications and while they perform their assigned functions well, they are difficult to adapt to new uses. There currently are no general purpose networks, rather there are telephone networks, low-speed data networks and cable television networks. As new communications applications proliferate, it becomes clear that in the long term, a more flexible communications infrastructure will be needed. The Integrated Services Digital Network concept provides a first step in that direction. We are concerned with the next generation of systems that will ultimately succeed ISDN.

The main focus of the effort in the ACS project is a particular switching technology we call broadcast packet switching. The key attributes of this technology are (1) the ability to support connections of any data rate from a few bits per second to over 100 Mb/s, (2) the ability to support flexible multi-point connections suitable for entertainment video, LAN interconnection and voice/video teleconferencing, (3) the ability to efficiently support bursty information sources, (4) the ability to upgrade network performance incrementally as technology improves and (5) the separation of information transport functions from application-dependent functions so as to provide maximum flexibility for future services.

## Acknowledgements

The Advanced Communications Systems Project operates within the Computer and Communications Research Center, an inter-departmental research laboratory in the School of Engineering and Applied Science at Washington University. The ACS project began on January 1, 1986 with support from Bell Communications Research and Italtel SIT. Additional funding is now provided by NEC and the National Science Foundation through grant DCI 8600947.

The Center's research program seeks an appropriate balance between theoretical and practical issues and has attracted considerable interest world-wide. Program sponsors interact with the Center through exchange of information and personnel. Our current sponsors are

National Science Foundation Bell Communications Research Italtel SIT Nippon Electric Corporation

We thank all our sponsors for their collaboration and support. Special thanks go to Gil Devey and Steve Wolf at NSF, Eric Nussbaum and Neil Haller of Bell Communications Research, Maurizio Dècina and Anna Robrock of Italtel and Akihiro Kitamura and Takehiko Yamaguchi of NEC. We also thank Washington University for providing an excellent environment in which to carry out this work, in particular Dean James McKelvey and Jerry Cox for all their support and encouragement.

# Contents

| 1 | Sur                                        | nmary of Progress                        | 1  |  |  |  |

|---|--------------------------------------------|------------------------------------------|----|--|--|--|

| 2 | Sw                                         | Switch Architecture Studies              |    |  |  |  |

|   | 2.1                                        | Comparison of Alternative Switch Fabrics | 13 |  |  |  |

|   | 2.2                                        | Refinements to the BPN Switch Fabric     | 22 |  |  |  |

|   | 2.3                                        | Design of Large Systems                  | 24 |  |  |  |

| 3 | Per                                        | formance Studies                         | 27 |  |  |  |

|   | 3.1                                        | Fluid Flow Loading Analysis              | 27 |  |  |  |

|   | 3.2                                        | Generalized Non-Blocking Networks        | 35 |  |  |  |

|   | 3.3                                        | Packet Misordering                       | 39 |  |  |  |

| 4 | Prototype Hardware Design                  |                                          |    |  |  |  |

|   | 4.1                                        | Packet Formats                           | 42 |  |  |  |

|   | 4.2                                        | Timing                                   | 46 |  |  |  |

|   | 4.3                                        | Packet Switch Element                    | 47 |  |  |  |

|   | 4.4                                        | Packet Processor                         | 54 |  |  |  |

|   | 4.5                                        | Broadcast Translation Circuit            | 60 |  |  |  |

| 5 | Tools for Design of Communication Circuits |                                          |    |  |  |  |

|   | 5.1                                        | Synchronous Streams Processors           | 63 |  |  |  |

|   | 5.2                                        | Implementation of SSPs                   | 66 |  |  |  |

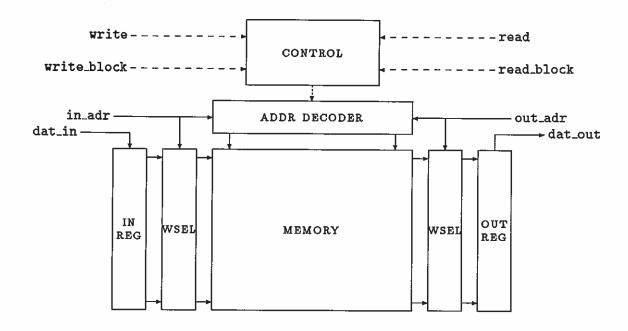

|   | 5.3                                        | Tools for Constructing Memories          | 68 |  |  |  |

|   | 5.4                                        | Other Tools                              | 69 |  |  |  |

| 6 | Co                              | Connection Management                     |     |  |  |

|---|---------------------------------|-------------------------------------------|-----|--|--|

|   | 6.1                             | Specification of Multipoint Connections   | 71  |  |  |

|   | 6.2                             | Multipoint Control Protocols              | 75  |  |  |

|   | 6.3                             | Prototype Connection Management Software  | 81  |  |  |

| 7 | Mu                              | ltipoint Routing                          | 83  |  |  |

|   | 7.1                             | Approximation Algorithms                  | 83  |  |  |

|   | 7.2                             | The Dynamic Steiner Tree Problem          | 87  |  |  |

|   | 7.3                             | Random Graphs and Probable Performance    | 90  |  |  |

|   | 7.4                             | Distributed Routing Algorithms            | 90  |  |  |

| 8 | Bandwidth and Buffer Management |                                           |     |  |  |

|   | 8.1                             | Queueing Behavior of Bursty Sources       | 94  |  |  |

|   | 8.2                             | Bandwidth Allocation                      | 96  |  |  |

|   | 8.3                             | Bandwidth Specification and Enforcement   | 98  |  |  |

|   | 8.4                             | Multipoint Congestion Control             | 99  |  |  |

|   | 8.5                             | Access Arbitration in Multipoint Channels | 103 |  |  |

| 9 | Pac                             | ket Video                                 | 107 |  |  |

# List of Figures

| 1.1 | Publications and Related Activities                    | 2 |

|-----|--------------------------------------------------------|---|

| 1.2 | Technical Reports                                      | 3 |

| 1.3 | Graduate Student Staff                                 | 1 |

| 2.1 | Broadcast Packet Switch Fabric                         | 4 |

| 2.2 | Starlite Switch Fabric                                 | 6 |

| 2.3 | Alternative Starlite-Type Switch Fabric                | 3 |

| 2.4 | Prelude Switch Fabric                                  | 0 |

| 2.5 | Local Switch Design                                    | 5 |

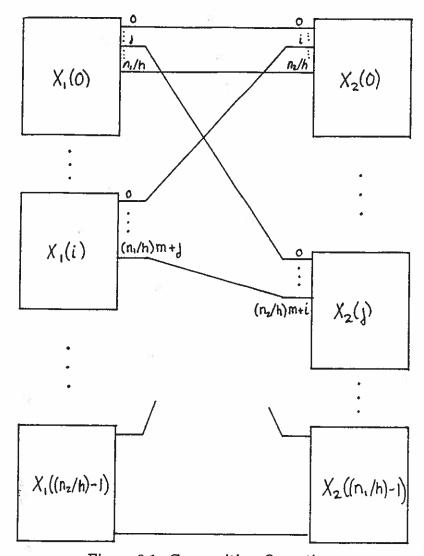

| 3.1 | Composition Operation                                  | 9 |

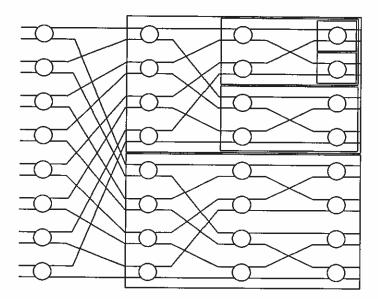

| 3.2 | Recursive Construction of Delta Network                | ) |

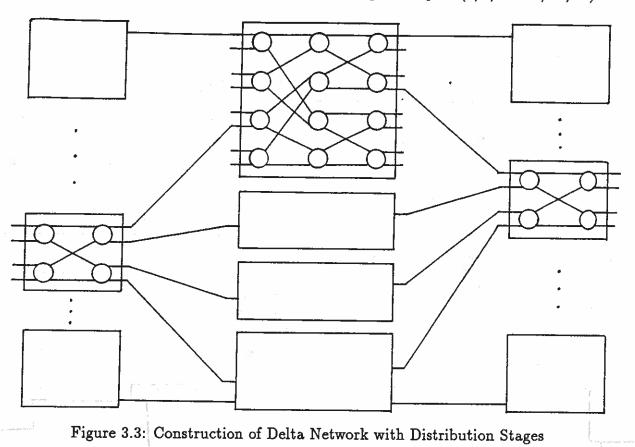

| 3.3 | Construction of Delta Network with Distribution Stages | 2 |

| 3.4 | Construction of Alternate Routing Network              | 3 |

| 3.5 | Worst-Case Configuration for Copy Network              | 1 |

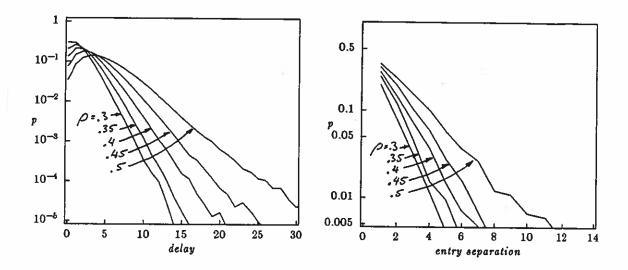

| 3.6 | Distribution of Delay and Misordering Probabilities    | ) |

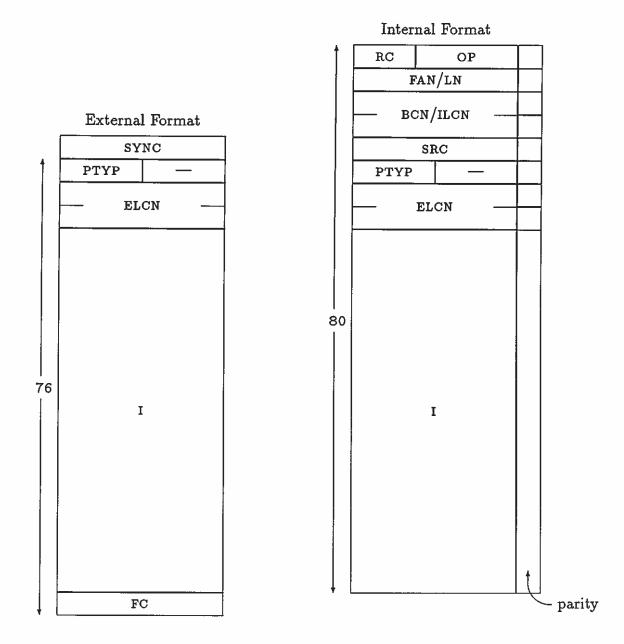

| 4.1 | Prototype Switch Module 42                             | 2 |

| 4.2 | Packet Formats                                         | ļ |

| 4.3 | Local and Global Timing Relationships                  | 7 |

| 4.4 | External Interface for Packet Switch Element Chip 48   | 3 |

| 4.5 | Block Diagram of Packet Switch Element Chip            | L |

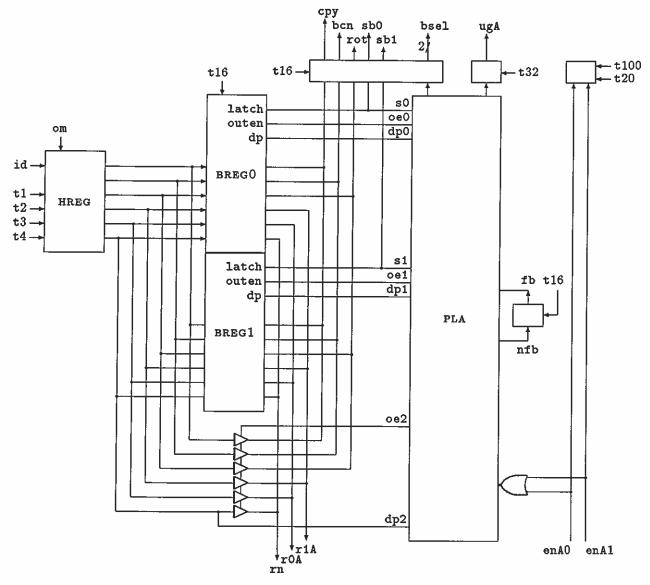

| 4.6 | Input Circuit                                          | 3 |

| 4.7  | Input Control Circuit                                                    | 55         |

|------|--------------------------------------------------------------------------|------------|

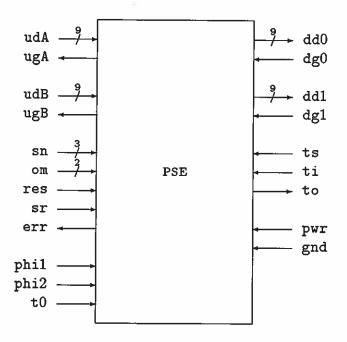

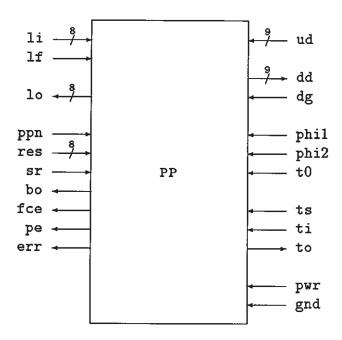

| 4.8  | External Interface for Packet Processor                                  | 56         |

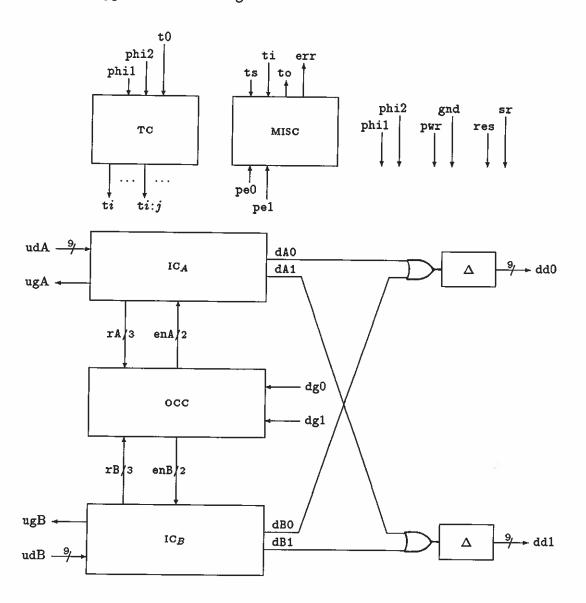

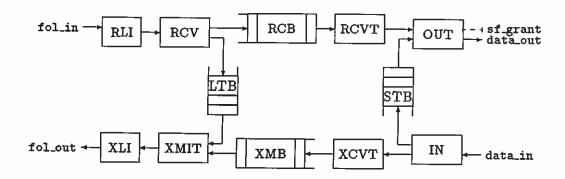

| 4.9  | Packet Processor Circuit                                                 | 57         |

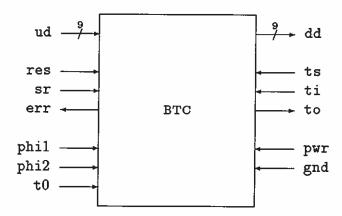

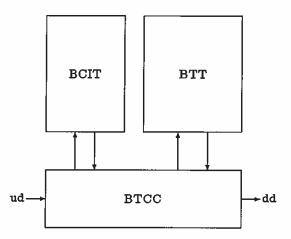

| 4.10 | External Interface for BTC                                               | 60         |

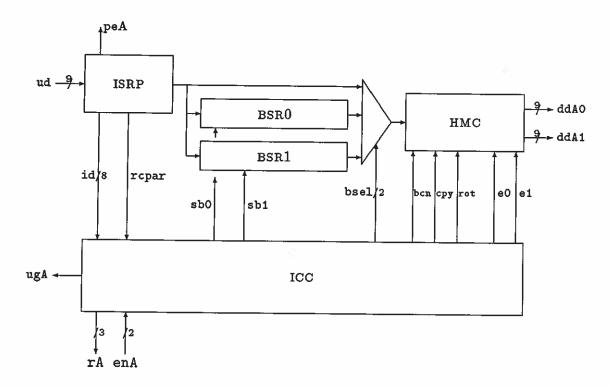

| 4.11 | Block Diagram of Broadcast Translation Chip                              | 62         |

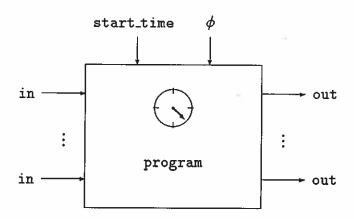

| 5.1  | Generic Synchronous Stream Processor                                     | 64         |

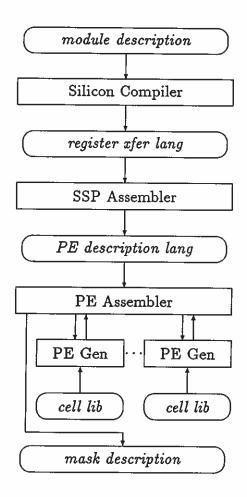

| 5.2  |                                                                          | 66         |

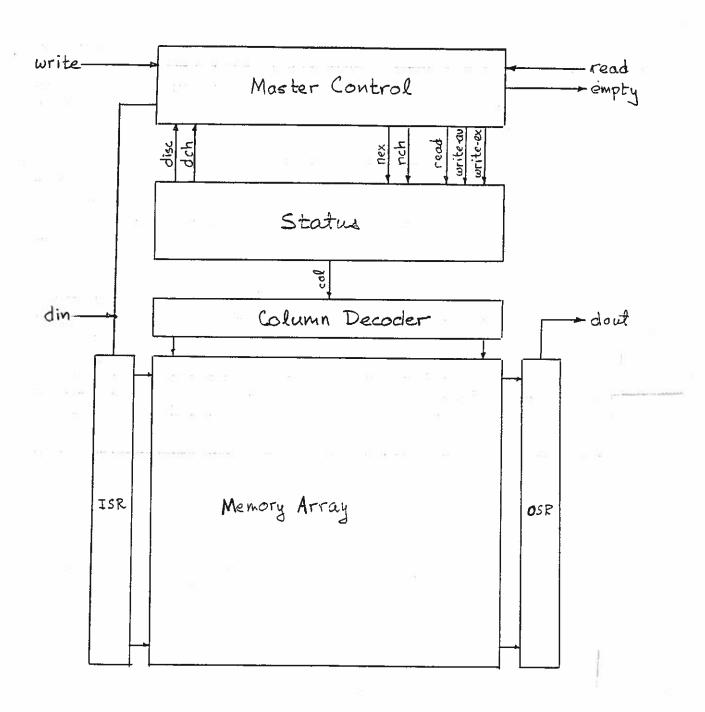

| 5.3  |                                                                          | 67         |

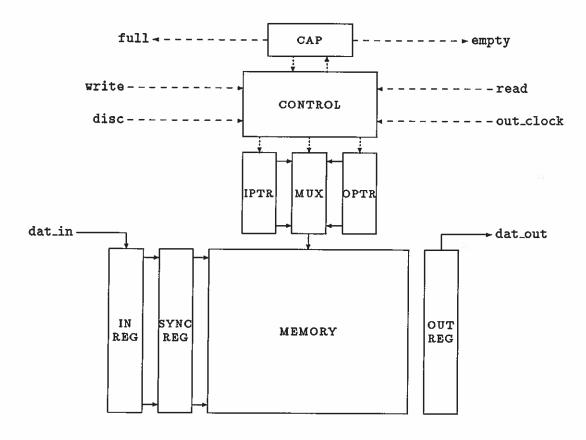

| 5.4  | Packet Buffer                                                            | 68         |

| 5.5  |                                                                          | 69         |

| 6.1  | One-to-Many Connection                                                   | 72         |

| 6.2  |                                                                          | 74         |

| 6.3  |                                                                          | 81         |

| 0.0  |                                                                          | <b>J</b> 1 |

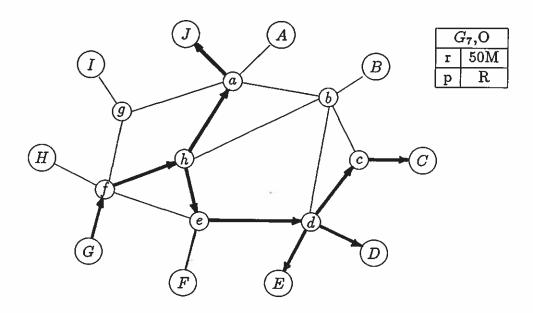

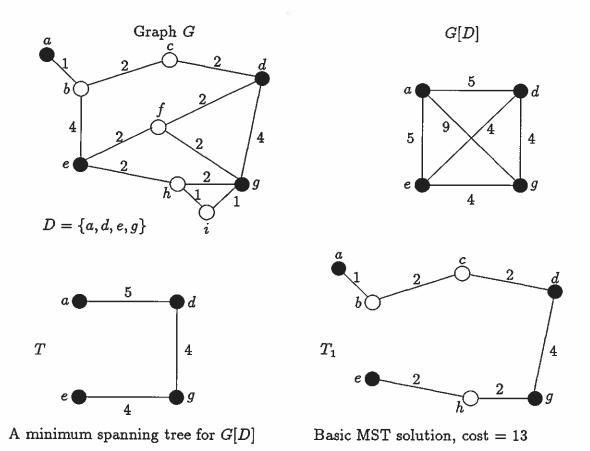

| 7.1  | An Example of the Application of MST                                     | 84         |

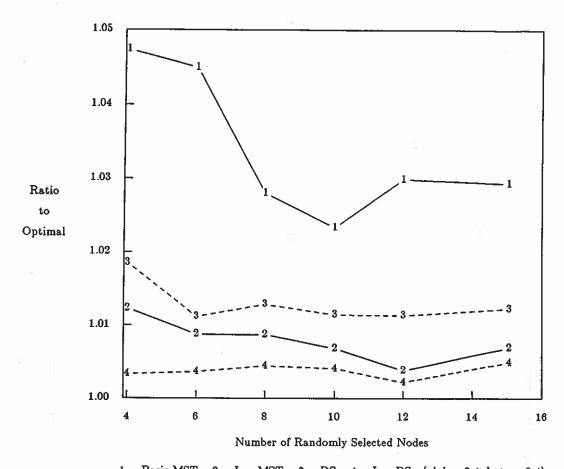

| 7.2  | Experimental Performance of MST and RS                                   | 85         |

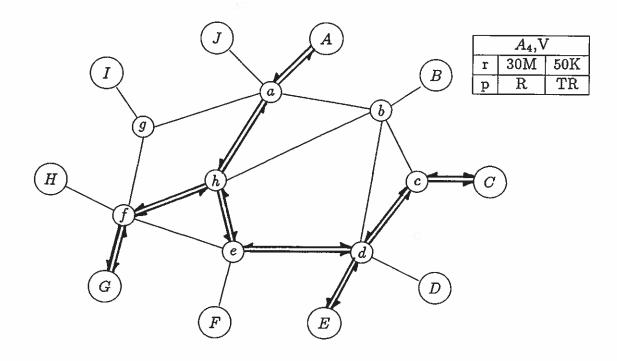

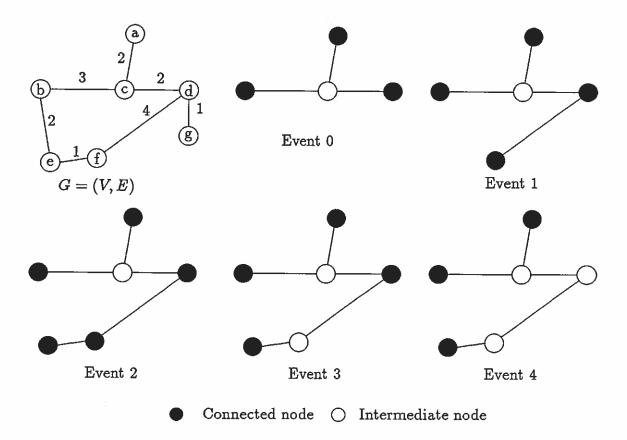

| 7.3  | Dynamic Greedy Algorithm with Sequence: a,b,d,f,e, $\bar{f}$ , $\bar{d}$ | 88         |

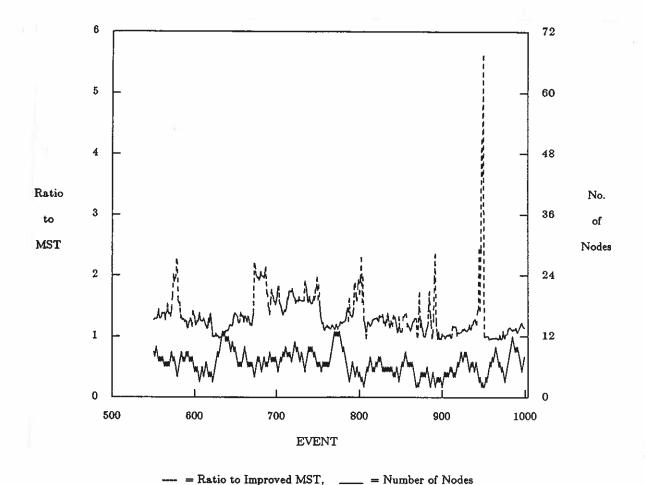

| 7.4  | Experimental Results for the Greedy Algorithm                            | 89         |

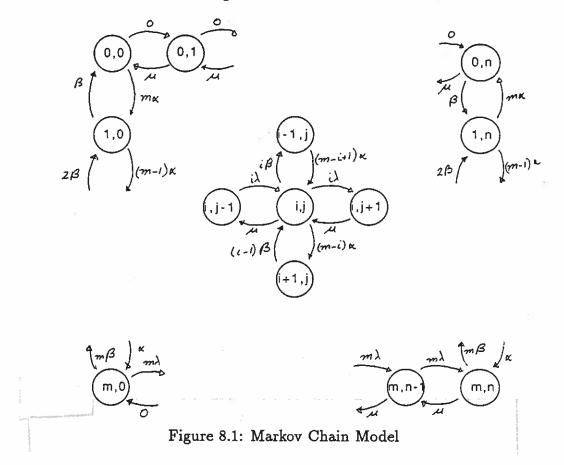

| 8.1  | Markov Chain Model                                                       | 95         |

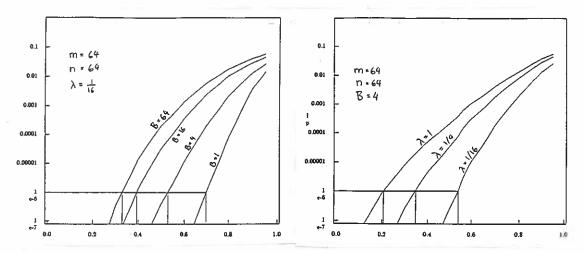

| 8.2  |                                                                          | 96         |

| 8.3  |                                                                          | 97         |

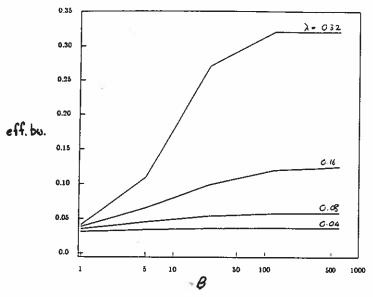

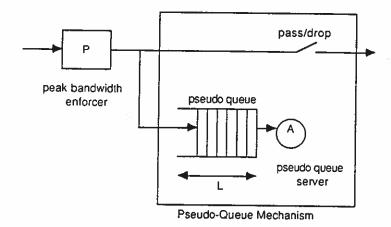

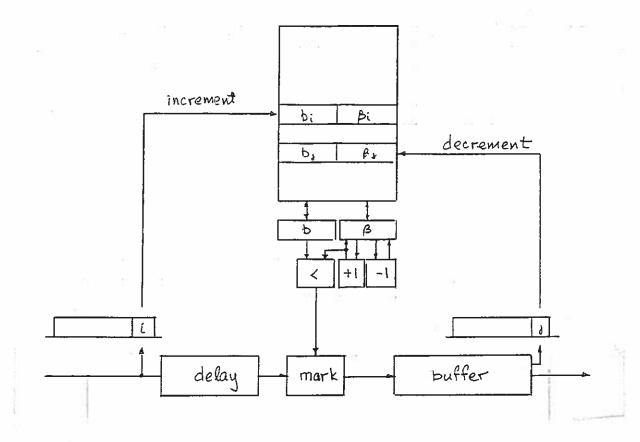

| 8.4  | Simple Bandwidth Enforcement Mechanism                                   | 98         |

| 8.5  | Buffer Management Mechanism                                              | )1         |

| 8.6  | Buffer Implementation                                                    | )2         |

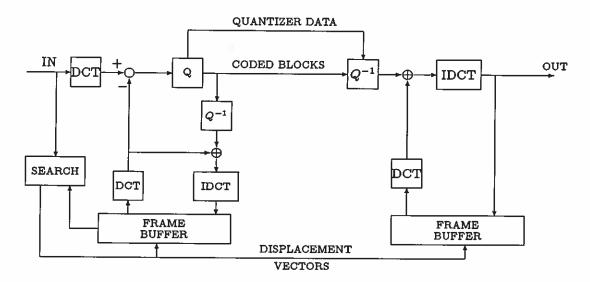

| 9.1  | Hybrid Video Codec                                                       | )8         |

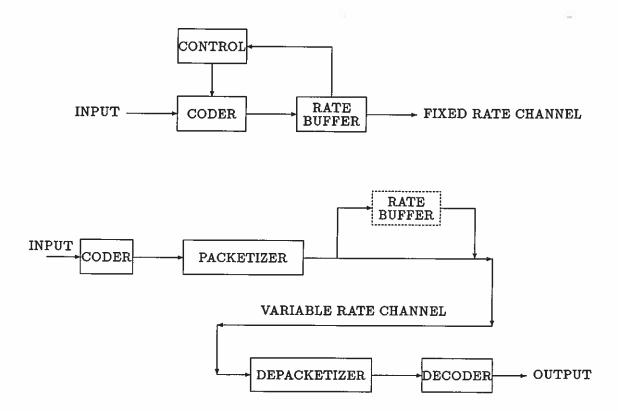

|      | Fixed vs. Variable Rate Channels 10                                      |            |

# 1. Summary of Progress

The research program of the ACS project can be divided into four major areas: (1) switching system architecture, (2) connection management, (3) network control problems, such as routing and congestion control and (4) design of communications applications in the context of broadcast packet networks. The primary focus of our effort in the last year has been switching system architecture, including the design of a prototype broadcast packet switch. In support of this prototyping effort we have also been developing tools to aid in the design of the custom integrated circuits to be used in the prototype. We have also made substantial progress on connection management, including the design and implementation of preliminary software, and we are continuing to make steady progress in the area of network control. Our work on application design is currently limited to an initial study of the issues associated with packetized video, focussing especially on the effect of packet transport on the design of video coding methods.

We have been active in publishing our results on broadcast packet switching. Papers have been presented at several conferences and revised versions have appeared or are scheduled to appear in leading journals. Patent applications have been filed on broadcast packet switching and invited lectures have been given at many industrial and academic laboratories. (See Figures 1.1,1.2 for details.) Our work has generated a great deal of interest throughout the world, and appears to be having an influence on the research programs at several major industrial laboratories. We find this impact of our work particularly gratifying and expect to see it continue as our research program develops.

The following subsections summarize the progress we have made in several specific areas during the past year and outline our plans for the coming year. More detailed accounts of each of these topics appear in later sections.

### Switch Architecture and Hardware Design

The most novel aspect of our research program is its focus on networks supporting flexible multi-point communication. Any switching system supporting multi-point

#### Published Papers

"Design of a Broadcast Packet Switching Network," by Jonathan S. Turner, Proceedings of Infocom 86, pp. 667-675, 4/86. Also, to appear in IEEE Transactions on Communications.

"New Directions in Communications," by Jonathan S. Turner, IEEE Communications Society Magazine, 10/86.

"Design of an Integrated Services Packet Network," by Jonathan S. Turner, IEEE Journal on Selected Areas in Communications, 11/86.

"Performance of a Broadcast Packet Switch," by Richard Bubenik and Jonathan Turner. Proceedings of ICC 87, pp. 1118-1122, 3/86. Also, to appear in IEEE Transactions on Communications.

"The Challenge of Multipoint Communication," by Jonathan S. Turner, Proceedings of the ITC Seminar on Traffic Engineering for ISDN Design and Planning, 5/87.

#### Invited Lectures

Telenet Inc., Reston, VA (8/87)

Southwestern Bell Telephone, St. Louis, MO (8/87)

Bell Atlantic, Great Gorge, NJ (2/87)

Midwest Workshop on Communications Systems, St. Louis, MO (11/86)

Computer Communications Workshop, Warner Springs, CA (9/86)

ITT Advanced Technology Center, Shelton, CT (9/86)

Tutorial on "Integrated Networks for Diverse Applications," at Infocom 87.

Program committee for ISS 87, ICC 87, Midwest Workshop on Communications Systems. Guest editor for special issue of IEEE Journal on Selected Areas in Communications

Course on switching systems (CS 577).

Figure 1.1: Publications and Related Activities

communication must be able to connect any subset of its incoming channels to any subset of its outgoing channels. This is in contrast to point-to-point switching systems which need only connect input-output pairs.

Our work is based on a particular switching system architecture for multipoint communication. During the past year we have also been studying some competing architectures, in particular the Starlite architecture based on Batcher's bitonic sorting network which is being developed at Bell Communications Research, and the Prelude system which is based on an extension of the classical time-slot interchanger design and is under development at CNET in France. Each architecture

3

"Performance of a Broadcast Packet Switch," by Richard Bubenik and Jonathan Turner, WUCS-86-10.

"An Architecture for Connection Management in a Broadcast Packet Network," by Kurt Haserodt and Jonathan Turner, WUCS-87-3.

"System Testing of a Broadcast Packet Switch," by Shabbir Khakoo and Jonathan Turner, WUCS-87-4.

"Specification of Integrated Circuits for a Broadcast Packet Network," by Jonathan Turner, WUCS-87-5.

"The Challenge of Multipoint Communication," by Jonathan Turner, WUCS-87-6.

"Design of a Broadcast Translation Chip," by George Robbert, WUCS-87-9.

"Thesis Proposal: Routing of Multipoint Connections," by Bernard Waxman, WUCS-87-10.

"Fluid Flow Loading Analysis of Packet Switching Networks," by Jonathan Turner, WUCS-87-16.

"Distributed Protocols for Access Arbitration in Tree Structured Communication Channels," by Riccardo Melen and Jonathan Turner, WUCS-87-17.

Figure 1.2: Technical Reports

has its respective advantages and disadvantages and none clearly dominates the others. Prelude and Starlite have two properties not shared by our architecture; they preserve packet sequence and they allow a single shared buffer. The ability to preserve packet sequence is potentially important for certain high speed applications. Shared buffering can provide substantially lower packet loss rates in the presence of highly bursty traffic. Some initial studies of these issues have already been made and they will be explored in detail in the coming year, first to assess their real importance, and second to identify extensions of the basic switch architecture that can address them.

Work on a laboratory prototype of our switching system was started about sixteen months ago, when we began design work on two integrated circuit chips. The first of the two chips is the packet switch element that makes up the copy, distribution and routing networks. This is a multi-function switch element that can be configured for any of the three networks, with two input and output ports per switch element. The second chip is the broadcast translation circuit which performs the translation for multi-point packets. It contains two random access memories implementing a pair of lookup tables controlling the translation process, plus associated control circuitry. The chips are being designed in a scalable CMOS

process with two layers of metal.

These preliminary designs have just recently been completed and submitted for fabrication. We are using our experience with these preliminary designs to guide us in the specification and design of the next set of chips that we will incorporate in our laboratory prototype. We also plan to design a two chip implementation of a packet processor and possibly a datagram router. These are being tackled in a broader context. We have found that several of the chips we need contain similar parts which are profitably viewed as special cases of a more general synchronous streams processor. We are developing a special-purpose silicon compiler that will take as input a specification of a streams processor and produce a description of a circuit implementing that specification. Substantial progress has been made on this program in the past year; the program is currently capable of producing simple circuits and we are confident that its use will significantly reduce the effort required for the design of several of the chips we require. It will also provide a powerful tool for the design of other similar chips. We have also recently begun related efforts which seek to automate certain portions of the design process for our prototype system.

### Performance of Packet Switching Fabrics

During the past year we have sought to extend our understanding of the performance of packet switching fabrics in general, with of course a special focus on the broadcast packet switch. One important result has been the development of a systematic method for analyzing the effect of different traffic patterns on the loading of internal links within a packet switching fabric. This method allows us to make statements about the worst-case loading of a variety of different switch fabrics. This has led to several new results quantifying the effect of distribution stages on switch fabric performance. One result shows that a k stage routing network requires an additional k-1 distribution stages in order to avoid overloading of internal links. Another shows that just two distribution stages dramatically improve the worst-case performance of copy networks. Other results concern the effect of the number of ports per node on worst-case loading. Of special interest is the observation that the worst-case performance of copy networks deteriorates as the number of ports per node increases.

We have recently been seeking to generalize the classical theory of non-blocking networks to networks in which internal links can multiplex multiple connections, with each connection consuming an arbitrary fraction of the link's capacity (subject of course to the constraint that the sum of the connection loads is no more than the link's capacity). This is relevant to the design of large switching systems constructed from multiple switch modules. It is also important for switch fabrics

which route all packets of a given connection along the same path, such as the systems under development at CSELT and Bell Telephone Manufacturing. Our initial results include an analysis of the amount of expansion required to make Clos and Cantor networks strictly non-blocking. We are also investigating the amount of expansion needed to obtain a rearrangeably non-blocking system and studying methods of analyzing blocking probability in such networks.

We have also made some initial simulation studies quantifying the likelihood of packets getting out of sequence when passing through a broadcast packet switch fabric. The results from these and planned further studies will be used to help in the design of mechanisms to recover proper sequencing.

### **Connection Management**

Connection management refers to the collection of algorithms used to create and maintain multi-point connections in a broadcast packet network. A multi-point connection is intended to be a flexible mechanism that can support a wide variety of different applications. To achieve this flexibility, it must be possible to configure a multi-point connection for different uses. One of the first challenges in creating a useful and practical connection management system is deciding exactly what set of primitive capabilities the network should provide to enable users to configure connections. The subsequent challenge is to design the mechanisms needed to implement these capabilities.

We have identified and refined a method of configuring connections based on the concepts of sub-channels within a connection and permissions. Sub-channels allow a connection to be broken down into several distinct information flows, which can be configured differently but because of their close relationships are controlled by the network in a unified way. Permissions give the user a mechanism for controlling access to sub-channels and assist the network in managing its resources (primarily trunk bandwidth).

Based on these ideas, we have developed a specification of a simple connection management architecture and a series of scenarios showing how it can be used to support a variety of applications including broadcast video and multi-media conferencing. The connection management architecture has been designed at several levels of abstraction, with explicit interfaces at each level. The primary abstraction level, from the user's perspective, is the one that defines the interface between the network and the user's termination controller. At this level, the network is viewed as a single entity which modifies connections in response to control messages. The next level of abstraction below this defines the interfaces between switching systems in the network and it is at this point that explicit reference

must be made to the distributed algorithms and data structures that implement the higher level abstractions. We have also been considering a higher level of abstraction corresponding to the interface between termination controllers. At this level application-dependent issues appear. Termination controllers cooperatively determine how connections should be configured to suit the client applications, and direct the network to configure them via control messages.

In the past year, we have developed an initial set of protocols supporting multipoint connections and implemented those protocols in the form of a software simulation that allows us to configure an arbitrary network, then set up and modify multi-point connections in that network. Our implementation of multi-point connections includes a general transaction mechanism for sequencing concurrent changes to a connection. We plan to use our current simulation to obtain a better understanding of the strengths and limitations of our current collection of protocols, including the transaction mechanisms on which they are based.

### Routing

The objective of the routing problem is to determine a set of network resources (primarily trunk bandwidth) sufficient to support communication among a specified set of users. In conventional circuit switched networks, all connections require the same amount of bandwidth and (almost all) have exactly two endpoints. Such a network can be described formally as a graph in which each edge has both a capacity and a length. A set of connections for such a network is simply a collection of vertex pairs. A feasible route assignment is an assignment of each connection to a path joining the connection's endpoints that doesn't exceed the capacity of any edge. An optimum routing algorithm is one that can find a feasible assignment whenever one exists.

Of course, this version of the problem is a static one. In a real communications network, the set of connections changes with time and the network must implement a routing policy that manages the changing set of connections in a way that makes it unlikely that a new connection will be blocked. In the interests of efficiency, it is generally assumed that once a connection has been assigned a route, that assignment will remain fixed as long as the connection is present. These considerations lead to a routing policy based on the heuristic strategy of routing connections by the shortest path available at the time the connection is established.

If connections can have an arbitrary bandwidth associated with them, the routing problem becomes a bit more complicated. One must now consider the network to be a graph in which vertices can be joined by multiple edges. To prevent blocking of connections with large bandwidth requirements, new connections should be

assigned to the fullest edges with sufficient capacity along the assigned route. This strategy preserves large blocks of bandwidth for use by high speed connections.

In broadcast networks, a connection can involve an arbitrary number of endpoints. A feasible route assignment for a set of connections is an assignment of each

connection to a subtree connecting its endpoints, in a way that does not exceed

the capacity of any edge. As in the case of point-to-point networks, connections

come and go over time, and so the appropriate routing policy is to assign each

connection to the subtree with shortest total length available at the time the connection is established. This can be viewed as a generalization of the Steiner tree

problem in graphs. This problem is known to be NP-complete, meaning that there

is unlikely to be an efficient algorithm that can always find an optimal solution.

On the other hand, there are several efficient algorithms that yield solutions that

are close to optimal. The best known one is called the minimum spanning tree

heuristic (MST).

Connections in broadcast networks are dynamic in another way. They grow and shrink with time as individual endpoints come and go. The challenge here, is to maintain a good connection topology without doing a great deal of recomputation each time an endpoint is added or dropped. Practical algorithms must be suitable for distributed implementation, with each node making decisions based on local information. The simplest algorithm is a greedy strategy that adds new endpoints by joining them to the connection by the shortest available path and dropping branches of the connection tree when endpoints drop out.

Our research objective is to develop practical and efficient algorithms that can be used in actual multi-point communication networks. To this end, we have been studying the performance of several approximation algorithms, including the MST and greedy algorithms, from both a worst-case and average case point of view. A prerequisite for our evaluation of the average case performance, has been the development of a simple probability model that can yield data relevant to real networks. We have developed such a model and have begun using it to evaluate the MST, greedy algorithms and others. We have shown experimentally, that the average case performance of the MST algorithm is excellent, usually within 5% of optimum. While this algorithm is probably impractical for application in a real network, our results show that it can serve as a useful standard of comparison against which other algorithms may be measured. In particular, we have used it to study the performance of the greedy algorithm in dynamically changing connections. Our results show that the solutions produced are generally within 20% of the value obtained for the MST algorithm. The performance deteriorates during long sequences of deletions, because the algorithm simply prunes rather than re-routing during such sequences. This sort of degradation is not unique to the greedy algorithm, but is intrinsic to any algorithm that makes only incremental

changes and does not re-route.

Our research plans include continued experimental evaluation of these algorithms and others. We have also begun to study the average case performance of these algorithms analytically, in order to obtain greater insight into the factors limiting their performance. We also plan to design and implement distributed versions of these algorithms.

### **Congestion Control**

A principal advantage of packet switched networks is their ability to dynamically allocate bandwidth to the users who need it at a particular instant. Since networks are subject to rapid statistical variations in demand, care must be taken to ensure acceptable performance under conditions of peak loading. Congestion control refers to the collection of methods used to ensure each user acceptable performance under a variety of load conditions. The high speed and multi-point connection capability of broadcast packet networks place new demands on congestion control methods.

A prerequisite to the development of an effective congestion control method is an understanding of the impact that bursty sources have on queueing in the network. The popular M/M/1 queueing model, while theoretically tractable and widely applicable, is insufficient to model the behavior of a small number of high speed and very bursty sources. A key part of our work in congestion control has therefore been to obtain an understanding of such sources. We are focussing on a simple model that treats each source as a two state Markov chain. The source is active in one state and idle in the other. Parameters of the model include average holding times in each state and the rate of packet transmission while active. This model can be used for a wide variety of bursty sources, including coded video. Our results to date indicate that such sources can lead to serious performance degradation if not handled carefully.

The basic congestion control mechanism under consideration involves user specification of several parameters defining peak and average bandwidth requirements, plus a measure of burstiness. The network uses these parameters to calculate an effective bandwidth, which is used for allocating link bandwidth. In the past six months we have developed a candidate method for computing effective bandwidths. This is based on the Markov chain analysis mentioned above, along with an interpolation scheme to permit rapid calculation in a realistic network context. We have found that for sources with peak and average bandwidths of more than a few percent of link bandwidth, the effective bandwidth is quite sensitive to how bursty the connection is, but for lower values, it is fairly insensitive. One implication of these studies is that to achieve effective bandwidths substantially lower than peak

for bursty, high speed sources we must either increase link speeds, buffer sizes or both.

The network also ensures that individual users don't exceed their specified rate, using a simple traffic valve at the edge of the network. One simple implementation of a traffic valve can be viewed as a pseudo-buffer for which the user specifies the peak arrival rate, the serving rate and the buffer size. Whenever the user sends a real packet, the network adds a pseudo-packet to the pseudo-buffer. If this does not cause the pseudo-buffer to overflow, the real packet is immediately accepted by the network. Otherwise it is discarded. (Note that only pseudo-packets go into the pseudo-buffer.) This mechanism is simple enough to be implemented within packet processor chips at the boundary of the network.

For multi-point connections with several transmitters, additional complications arise, since the control of entering traffic provided by the traffic valves at the edge of the network allows excess traffic on internal links of multi-point connections. We have designed a mechanism to control this kind of overload, which in effect allocates link buffer space in direct proportion to bandwidth allocations, and discards packets belonging to connections that exceed their share. This mechanism, in combination with others we have developed, allows a general solution to the problem of multi-point congestion control.

We have also considered a different approach to multi-point congestion control, in which the network actively controls the number of simultaneous transmitters in a multi-point connection, rather than limiting itself to the protection of its internal resources. This kind of access arbitration could be more attractive to users, as it regulates the flow of traffic on a channel in a more consistent fashion. We have developed two general approaches to access arbitration, and several specific algorithms.

#### Packet Video

Packetized transport of video signals raises a variety of important issues that we are beginning to explore. One major effect of packet transport on video coding is to eliminate the constraint of a constant bandwidth channel that currently drives most work in video coding. A variety of techniques including transform coding, motion compensation, differential coding and adaptive quantization are currently used to reduce the required bandwidth for video signals. Existing systems use buffering and variable rate coding, with the objective of achieving minimum image distortion for a given, fixed channel bandwidth. In the context of packet transport, we can exchange the objective function we seek to optimize with the constraint. That is, we code to achieve minimum bandwidth subject to a given constraint

on distortion. This approach allows the bandwidth to vary across a wide range, achieving low average bandwidths and high picture quality.

Packetized transport also raises the issue of picture quality in the presence of packet loss. Common video coding methods rely heavily on state information that can become inconsistent when data is lost. The impact of lost packets can be reduced by interpolation schemes, in which a given block of information is split across multiple packets, allowing partial recovery of lost information. We expect that the use of such methods in combination with low rate transmission of complete state information can maintain high picture quality in the face of substantial packet loss rates and we are studying such methods to assess their potential.

Historically, video coding methods have been used primarily to produce moderate quality video for conference applications. With high speed packet networks it may also be advantageous to apply video coding methods to very high resolution signals; the objective becomes not bandwidth reduction but higher resolution. This raises some interesting issues in codec design. Current codecs can be built with limited parallelism because of the low resolutions and data rates that they must cope with. Codecs for high resolution video will require greater parallelism and greater reliance on custom integrated circuits.

### Administrivia

In the past year, we have grown from a small base to a research team that now includes two faculty members, one full-time staff person, one visiting research associate and nine graduate students. Additional faculty are also being recruited in both the Computer Science and Electrical Engineering departments, and this will have an important impact on the project. One recent addition to the Computer Science faculty is Gurudatta Parulkar who has just graduated from the University of Delaware. Dr. Parulkar's thesis research focussed on the design and analysis highly reliable local area networks based on flooding protocols. We expect him to be an important collaborator for the ACS project.

Our funding picture is fairly healthy. In addition to the support we receive from our three corporate sponsors, we have a major grant from the National Science Foundation that currently provides about 60% of our funding. In addition to the direct grant support, NSF provides access to MOSIS, their silicon fabrication service which we are using heavily in our prototyping effort. We have recently benefitted from a change in the policy of the Washington University School of Engineering and Applied Science; the school now pays the tuition of graduate students on research assistantships rather than requiring the research grant to pay that portion. This change has allowed us to increase our graduate student stipends

| Name               | Degree (exp. graduation date) | Research Area                |

|--------------------|-------------------------------|------------------------------|

| Shahid Akhtar      | MS (10/87)                    | congestion control           |

| Neil Barrett       | MS (5/89)                     | communication circuit design |

| Victor Griswold    | DSc (1/90)                    | connection management        |

| Mark Hunter        | MS (5/88)                     | connection management        |

| Shabbir Khakoo     | MS (5/88)                     | packet video                 |

| George Robbert     | MS (5/88)                     | CAD tools                    |

| James Sterbenz     | DSc (1/90)                    | communication circuit design |

| Bernard Waxman     | DSc (1/89)                    | routing                      |

| Einir Valdimarssen | MS (5/89)                     | communication circuit design |

Figure 1.3: Graduate Student Staff

which have been low with respect to other schools with which we compete. We have also used some of the funds made available by this change to improve our base of computing equipment.

While the project's funding situation is in fairly good shape at the moment, we anticipate that additional funding will be required if we are to achieve all our major goals. The most likely source of new funding in the short term is through expansion of the Consortium to five or six members. We are currently exploring the possibility of consortium membership with three new companies. Such expansion could provide adequate funding through September 1989. After that time, substantial new funding may be required. We are beginning to explore possible sources of that funding including an NSF Engineering Research Center grant.

The project currently supports professors Jonathan S. Turner and Mark Franklin (part-time) plus eight graduate research assistants (see Figure 1.3). We have one additional student (Akira Arutaki) who is supported by NEC. We expect to add between one and three additional graduate students in the coming year. In addition, we have one professional staff member (Pierre Costa) and one visiting research associate (Riccardo Melen).

For administrative purposes, the ACS Project operates within the Computer and Communications Research Center directed by Professor Mark Franklin. The Center has a central office suite housing professors Franklin and Turner, plus eight graduate students, on the third floor of Bryan Hall, across from our main laboratory facility. This laboratory houses our main computers, and a cluster of terminals and workstations for graduate student use and also serves as an informal meeting room.

We have a second laboratory on the fifth floor of Bryan which is devoted to our hardware prototyping efforts. Over the summer, we acquired additional space on the fifth floor of Bryan adjacent to the laboratory, which has been converted to office space.

The Center's base of equipment includes a VAX 750, a MicroVax II/GPX and a Sun 3/280, all running Unix. The MicroVax is used primarily to support VLSI design work. The Sun is a recent addition and is used primarily as a file server for five Sun 3/50 workstations we have also just acquired. We have about fifteen conventional terminals, a second VLSI design station, and assorted printers. We also have assorted lab equipment including a Tektronix logic analyzer and IC tester.

We have been generally successful in expanding the Center's space and facilities to meet our needs. As we are not planning substantial additional growth in the immediate future, we feel reasonably comfortable with the current situation. On the other hand, space shortages may develop in the next year as the Computer Science and Electrical Engineering departments continue to expand their faculties. While the Engineering School is planning a new building which will relieve the space shortage in the long terms, temporary steps will undoubtedly be required in the interim.

# 2. Switch Architecture Studies

Faculty

Mark Franklin Jonathan Turner

Research Associate

Riccardo Melen

Graduate Student

James Sterbenz

The architecture of high speed packet switching fabrics is of course central to the work of this project. While we are concentrating our efforts on a particular design [59], we continue to evaluate alternatives, in order to identify possible improvements. In the past year, we have made a close study of two alternative architectures for fast packet switching that are being developed by other research groups. Our objective in this study has been to understand the similarities and differences among the different fabrics and make a preliminary assessment of relative strengths and weaknesses. We hope to use the insights gained in this way to obtain better designs.

This chapter has three main sections. The first summarizes our comparisons of the broadcast packet switching fabric [59] with the Starlite [26,27,28] and Prelude [7,14,22] switch fabrics. The second outlines some possible improvements to the broadcast packet switch fabric that were suggested by our comparative studies. The third outlines some of the issues associated with constructing very large switching systems from modules of moderate size. We close with a summary and brief discussion of our research plans.

### 2.1. Comparison of Alternative Switch Fabrics

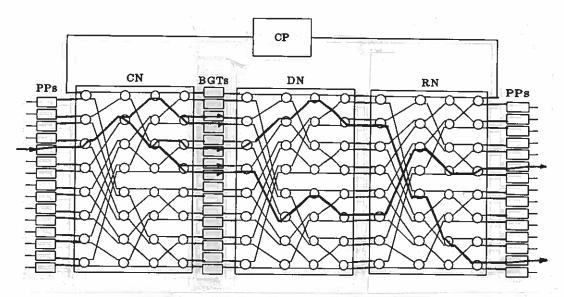

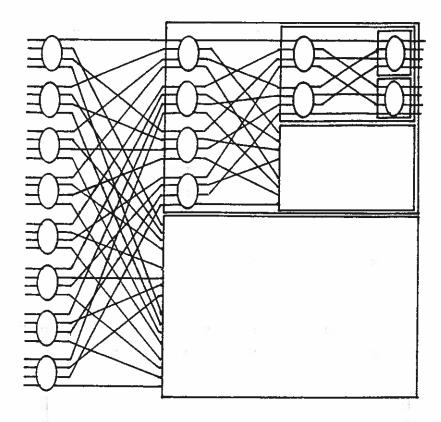

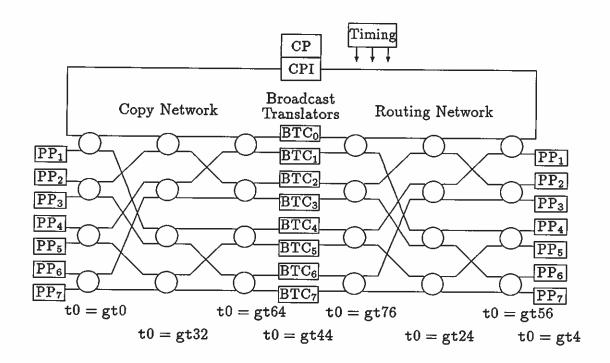

The switch fabric for the Broadcast Packet Network (BPN), described in [59] is based on buffered binary routing networks. It is topologically simple and well-suited to VLSI implementation. The overall structure is shown in Figure 2.1. The system consists of a set of *Packet Processors* which interface to the external links and provide all per packet protocol processing, a *Connection Processor* which sets

Figure 2.1: Broadcast Packet Switch Fabric

up and maintains multipoint connections, and a switch fabric consisting of a Copy Network, a set of Broadcast and Group Translators, a Distribution Network and a Routing Network.

Packets enter one of the Packet Processors at left, where an address translation is performed. For point-to-point packets this yields an outgoing link number and an outgoing channel number. These are placed in the header of the packet, which then passes through the CN, one of the BGTs and the DN, following some arbitrary path. When the packet reaches the RN, it is routed using the outgoing link number. The RN is a conventional binary routing network with sufficient storage at each node to store a small number of complete packets. When the packet reaches the outgoing PP, the extra header information added at the incoming PP is stripped off and the packet is transmitted on the outgoing link. The role of the DN is to randomly distribute packets it receives across its outputs. This prevents congestion that can otherwise occur in the RN when subjected to traffic patterns with strong "communities-of-interest."

When a packet belonging to a multipoint connection is received at an incoming PP, it undergoes a similar translation process, but the information added to the packet header is different. It consists of two fields, a Fanout field which specifies the number of outgoing links which are to receive copies of the packet, and a Broadcast Channel Number, used by the BGTs. The CN replicates multipoint packets using the fanout field to guide its decisions. At each switch element where replication is performed, the fanout fields of the two copies are modified (essentially by halving the original fanout), so that a short time after the original packet enters the CN,

the appropriate number of copies appears at its outputs. The BGTs then perform a translation similar to that done in the PPs, using the broadcast channel number in the copies to index a table, yielding a set of outgoing link and logical channel numbers. These are added to the packet header and used to guide the copies to the proper outgoing links.

This design is well-suited to implementation in a medium speed, high density technology like CMOS. While the per node buffering makes the individual switch elements moderately complex, the topological complexity is very low. The only large memories are in the PPs and BGTs, and these need be accessed only once per packet cycle, permitting the use of high density memories with relatively long cycle times.

In the last five or six years, several experimental switching system designs have been proposed that can support multirate and multipoint communication in a flexible fashion. In addition to the BPN fabric being designed at Washington University, there is the Starlite system originally developed by Alan Huang and Scott Knauer at AT&T Bell Labs and currently being developed further by a group at Bell Communications Research, and the switching matrix for the Prelude experimental wide band switching system, developed by Coudreuse et. al. at CNET in France. Starlite and Prelude are described below.

### Starlite

Starlite is the name given to an experimental switching system developed by Alan Huang and Scott Knauer at AT&T Bell Labs [26,27,28]. The Starlite architecture was motivated by the observation that sorting networks, can be used to construct rearrangeably non-blocking switching fabrics with distributed control. This observation was first put forward by Batcher [2] in 1968 in his seminal paper describing his bitonic sorter that sorts a set of n numbers using a network of approximately  $(n/4)(\log n)^2$  simple comparison elements. For circuit switching applications, this observation leads to switching networks that are non-blocking, operationally very simple and eminently suited to VLSI implementation. To accommodate packet switching, mechanisms are needed to resolve contention between packets that arrive concurrently and are destined for the same output port. Multipoint communication requires additional mechanisms for packet replication. Huang and Knauer's contribution was the development of inexpensive VLSI implementations of Batcher's sorting network and the invention of a variety of supplementary networks which support packet switching and multipoint communication when used in concert with the sorting network. More recently, a group at Bell Communications Research has adopted Starlite as the basis of a major applied research effort in high speed packet switching and have devised a number of improvements. In this section, we first

Figure 2.2: Starlite Switch Fabric

describe some of the original work on Starlite done at Bell Labs. We will then review some of the more recent improvements.

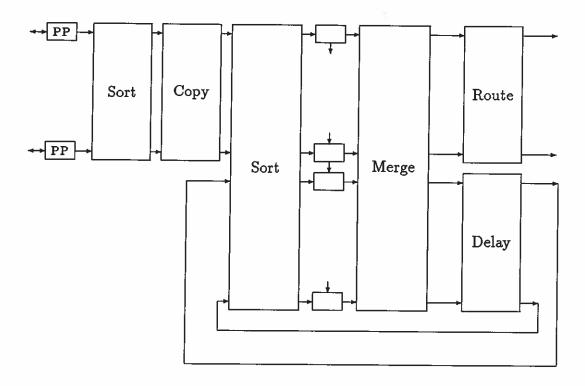

While Huang and Knauer made no serious attempt to develop complete systems, they did develop a variety of useful tools that can be used for the construction of such systems and suggested ways in which they could be used. Figure 2.2 shows one possible implementation of a packet switch supporting multipoint communication. Packets arriving on external links enter a set of *Packet Processors* at left, which perform some address translation. For point-to-point packets this results in a destination PP number being placed in the packet header. This is used to guide the packet to the appropriate outgoing link.

For the moment, we will ignore the initial sort and copy networks at the top left and concentrate on what happens to packets when they enter the main sorting network at the middle of the figure. This network sorts packets in increasing order of their destination addresses, meaning that when the packets exit the sorting network, all packets with same destination address occupy a contiguous set of output links. The filters at the exit of the sorting network mark all but one packet destined for a particular address, by comparing the destination addresses

of packets on adjacent links; if a packet has the same destination address as the packet on the next lower link, its wait bit is set. Packets for which the wait bit is zero are forwarded to the routing network at right which routes them to the proper outgoing links. Packets with the wait bit set are sent to one of a set of delay elements, which delays them for approximately one packet time, after which they are recirculated through the sorting network. It's useful to extend this basic scheme by adding a second field to each packet which records the number of times a packet has recirculated. By having the main sorting network use this field as a secondary sort key, we can also order packets by their age, giving older packets priority over newer ones. This ensures that packets are transmitted in the same order in which they were received. If the network supports n external links and the main sort and merge networks have m input and output ports, up to m-n packets may be recirculating at any time. Packets may be lost if during a cycle, more than m-n packets have their delay bits set. The value of m is selected based on statistical considerations, to yield an acceptably low probability of packet loss.

We now turn to the issue of packet replication. The network is designed around the notion of a coordinated copy between source and destinations. That is, the source and the destinations must synchronize when a packet is to be copied. When the source PP sends a packet into the network, the destination PPs simultaneously send blank packets containing their address plus the address of the source in the headers. The initial sorting network sorts these packets on the source addresses, which places the original packet and associated blank packets on a contiguous set of links, upon exit from the sorting network. The copy network then copies the information from the source packets to each of the blank packets, a relatively straightforward process, given the sorted arrangement. When these packets enter the main sorting network, they are routed using destination addresses in the same way as point-to-point packets.

The Starlite system has some very attractive properties. The basic switch elements making up the various networks are simple and have a regular interconnection pattern, which makes the design of high speed VLSI implementations quite straightforward. The network is non-blocking and has a latency of only one bit time per stage of switching. It maintains packet sequencing, so that packets are received in the same order in which they are transmitted. The sharing of buffering across the switch fabric, rather than dedicated it to individual links provides more predictable performance in the face of statistical fluctuations in traffic.

The synchronization required for copying is a drawback of this approach, when used in a general packet switching environment. Some form of arbitration is required at the front end to schedule packets that must be copied, and while such a mechanism is probably feasible, no detailed proposal has been put forward. Also, while the switch elements are very simple, their interconnection is topologically

Figure 2.3: Alternative Starlite-Type Switch Fabric

complex relative to competing proposals. Finally, the dimensioning of the main sort and merge networks is problematical; it appears likely that to achieve satisfactory performance in a general packet switching environment, these networks must have at least four to eight times as many inputs as there are external links. Nevertheless, the Starlite approach is a very promising one, and is a convincing demonstration of the power of a few simple ideas.

The many attractive features of Starlite have led a group of researchers at Bell Communications Research to use it as the basis for their work on high speed packet switching. This group has substantially extended the work of Huang and Knauer in a number of ways and have developed better or more complete solutions to the problems of output contention and packet replication. We briefly describe one possible system configuration based on their work. The reader is referred to references [9,38] for further details.

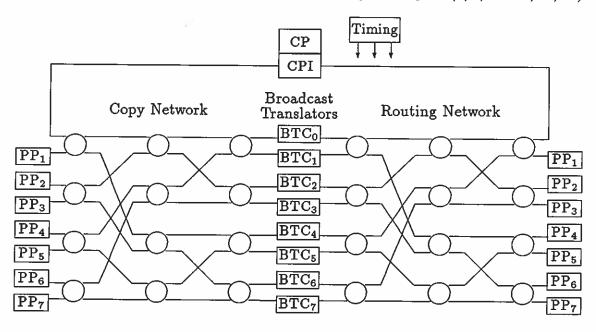

Figure 2.3 shows a switching fabric with several components. Packets are received at the Packet Processors (PP) on the left where they are assigned a fanout and broadcast channel number, as in the BPN fabric. The packets then pass through a concentrator network (consisting of  $n \log_2 n$  simple switch elements), which places the packets on consecutive outputs so as to ensure non-blocking operation of subsequent networks. Next, the packets pass through a running adder network, which for the packet on output port i computes the sum of the fanouts of all packets entering on ports 0 through i-1 and places this sum in a field of the packet (this is done for all output ports, using a network with  $n \log_2 n$  simple processing elements). Following the adder, the packets pass through a copy network which uses the fanout and the sums generated by the concentrator to generate the proper number of copies. Note that during any one cycle, the packets entering may have

a total fanout larger than n. The system accommodates as many packets as are feasible and the PPs resubmit 'losing packets' on the next cycle. Note that there is no internal buffering in the fabric. The specific mechanisms employed ensure that blocking cannot occur due to contention for internal paths within the fabric.

After the packets emerge from the copy network, they are processed by a set of broadcast translation circuits, which assign outgoing link numbers to each packet, as in the BPN system. Unlike the BPN system, each broadcast translation circuit here must be able to route any one of the copies of a broadcast packet, implying a substantial expansion in the memory requirements.

The packets then enter a set of queues, followed by a sorting and routing network. The sorting network routes packets on destination address and the routing network then routes them to the proper output once they are in sorted order. The queues are interconnected by a control ring which arbitrates access to switch fabric output ports. The control ring has a bit for each output port and a queue which has a packet to send to a particular output port signals its intention by setting the bit corresponding to that port. Since the control ring circulates through the queues sequentially, only one queue is permitted to send a packet to a particular output port during a cycle. The use of the control ring eliminates output contention and consequently, the potential for internal congestion in the routing network.

This configuration offers a complete solution to the problem of multipoint packet switching. The most complex single element is the sorting network; the other components together are roughly equal to the sorting network in complexity for networks with 1024 input and output ports. While substantially less complex then the first architecture described, it lacks the advantage of shared buffering. It also introduces the potential for packets to be misordered, since consecutive packets in a connection may be placed in different queues following the BTCs.

### Prelude

The Prelude project began at CNET in France in the early eighties, with the objective of creating a flexible switching system that could provide point-to-point and multipoint communication at speeds up to a few hundred megabits per second [7,14,22]. It is based on a particularly simple form of fast packet switching referred to as asynchronous time division multiplexing, and uses a novel high speed switch fabric.

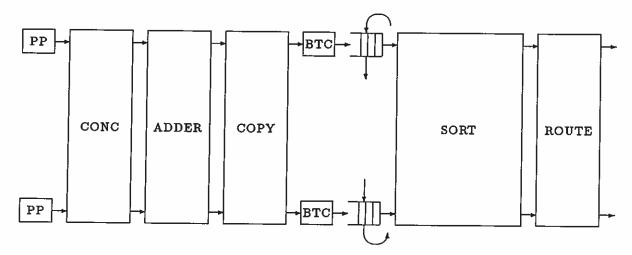

The basic structure of the Prelude switch fabric is shown in Figure 2.4. Packets enter at the transmission interfaces at left, which perform framing and synchronization functions. The packets are then passed through a rotative switch which transforms each packet to a so-called parallel-diagonal format (paragonal) in which

Figure 2.4: Prelude Switch Fabric

each packet is distributed across the outputs of the rotative switch, with the first byte of each packet on the first output, the second byte on the second output, and so forth. This transformation places the headers of all packets on the first output of the switch, where they can all be processed by a centralized address translator. The address translator modifies the channel number in the header of the packet and then the modified packet is stored in a central buffer memory, still in the paragonal format. At the same time, the address translator passes to the output control circuit, a bit vector defining which outputs are to receive copies of the packet. The output circuit stores the address at which the packet header was written, in queues associated with the selected outputs. This information is used later to retrieve the packet from the central buffer. There is an output process that examines these queues in a cyclic fashion, initiating a new packet retrieval on each clock cycle. Broadcast is accomplished simply by reading the packet from the buffer once for each output that requires a copy. Note that these reads need not all take place during one packet cycle. Finally, a second rotative switch transforms the packets from the paragonal format back to the normal format so that they can be output on their respective links.

This design has several attractive features. The basic elements are simple; the rotative switches can be implemented as barrel shifters, requiring about  $n \log n$  gates, the address translator and buffer are essentially just random access memories with a modest amount of control circuitry, and the output control consists of a fairly simple and regular collection of queues and address registers. As with Starlite it maintains packet sequencing and provides a single shared buffer rather than

per line buffers. It is, on the whole simpler than the Starlite fabric and handles multipoint communication in a more satisfactory way.

The main drawback of this approach is its dependence on high speed memories, particularly in the central buffer. It must be possible to access this memory twice per clock time, once for reading and once for writing. There does not appear to be any architectural way to reduce the required memory cycle time for individual memory chips since the memory read-out process can access the memory chips in random order. Another drawback is that since channel translation takes place before packets are replicated, all the downstream copies of a multipoint packet carry the same channel number. This places operational restrictions on the assignment of channel numbers, that may be problematical, depending on the number of channels and multipoint connections. It is most troubling for general multipoint connections in which there are several transmitters. It appears that either all the links involved in such a connection must use the same channel number, or there must be a different channel number for every incoming port that can be the source of the packet. The latter solution requires that the downstream switches treat all those channel numbers similarly.

### Remarks

One major difference between the BPN approach and Starlite and Prelude, is the use of buffering within the switch fabric. While this leads to more complex switch elements, the added complexity has little impact on cost or performance. The reason is simply that cost is determined primarily by component count, which because of pin limitations is determined primarily by topological complexity, not circuit complexity. While simple switch elements are better suited to low density technologies such as ECL, they have little advantage in the context of a high density technology like CMOS. Furthermore, the packet processors required in all three systems, have inherently high circuit complexities and must be implemented in high density technologies to be economical.

Starlite and Prelude do have two potentially significant advantages over the BPN approach. First, they can both implement shared buffering, leading to more predictable performance in the presence of highly bursty traffic. While the addition of some shared buffering to the BPN fabric is feasible, no detailed study of such an arrangement has yet been made.

Starlite and Prelude also guarantee that packets are transmitted in the same order as they are received. While it is possible to modify the BPN design to provide a similar guarantee, the required changes may impose operational constraints and degrade performance.

This brief review leads to three conclusions. First all three of the switch fabrics reviewed are viable architectures; they can all be used to support high speed packet networks and multipoint communication in an effective way. Second, none clearly dominates the others; each has a different set of advantages and drawbacks. Third and perhaps most important, each offers some useful lessons to architects of future systems. In the next section, we consider some of the ways in which these lessons might be applied.

### 2.2. Refinements to the BPN Switch Fabric

We now briefly consider several key architectural issues that will be addressed in the coming year. The first is the problem of resequencing packets; second is the issue of shared buffering; third, a potential application of partial sorting to the BPN fabric; and fourth, some issues that arise in the design of very large systems.

### Resequencing

The design of the BPN switch fabric allows packets belonging to a particular logical channel to exit the fabric in a different order from the order in which they are received. We briefly consider several alternative methods for dealing with this problem.

The first method is not to allow packets to get out of order in the first place. This is the approach taken by Starlite and Prelude and can be adopted with the BPN fabric. The key is to distribute traffic in the CN and DN on a per channel basis rather than a per packet basis. This complicates the hardware slightly and the control software substantially. It also introduces the possibility of a connection blocking when a path with sufficient capacity cannot be found. This approach is being taken by a group at CSELT in their fast packet switching research project.

A second method is to allow resequencing to be done on an end-to-end and application-dependent basis. Preliminary performance data indicate that the probability of packets arriving out of order is extremely unlikely for applications with peak data rates of less than 20% of the FOL data rates. The reason is simply that the time between arrivals of successive packets at a switch is larger than the time it takes a packet to propagate through the switch fabric. Only applications with very high peak data rates are expected to experience a significant rate of packet misordering. This implies that the majority of applications can ignore the resequencing problem and suggests that the provision of a general mechanism for handling it may be unwarranted. Applications such as video or file transfer can

handle the resequencing problem in a simple and straightforward way (for video, for example one merely places received packets in the proper position in the frame buffer based on a sequence number).

Resequencing can also be done on an end-to-end, application-independent basis. The most general solution requires buffering and a retransmission protocol. A simpler method is possible if one is willing to tolerate a small but non-zero probability of misordered packets (e.g 10<sup>-6</sup>). To provide such a guarantee, one adds sequence numbers to packets as they enter the network and uses the sequence numbers to resequence packets on exit. The resequencing device buffers packets as necessary, but never holds a packet longer than a specified time. The amount of buffering required and the timeout value depend on the misordering probability of the network and on the target residual misordering probability. Resequencing can also be done on a per switch basis. The method is similar to the end-to-end, application-independent method but is somewhat simpler to implement.

Detailed evaluation of these options has not yet been attempted. The circuit complexity and performance of end-to-end and per-switch resequencing in particular, requires closer study.

### Shared Buffering

While the FOL switch fabric contains buffers, which can in some sense be viewed as shared, most of the buffering actually occurs in the outgoing packet processors. For traffic with Poisson arrival statistics, per-link buffers with 64 buffer slots are sufficient to achieve packet loss rates (due to buffer overflow) of well under  $10^{-6}$  at link occupancies of 80%. Unfortunately, many real applications have arrival statistics that are highly non-Poisson. For these bursty applications, larger buffers or lower link occupancies are required for satisfactory packet loss rates.

One way to achieve the effect of larger buffers is to provide the buffering on a shared basis as done in Prelude and Starlite. For the BPN fabric, a set of shared buffers can be placed between the distribution and routing networks, with a hardware mechanism used to control the flow of packets from the shared buffer. A simple way of implementing this control is to provide a simple TDM control ring, that carries one bit of flow control information from each PP to each of the shared buffers. This is similar to the use of the control ring in the alternative version of the Starlite fabric described above.

While shared buffering appears to be worthwhile, the situation is really less clear than it might seem. One of the advantages of per-link buffering is that it puts an upper bound on the queueing delay at each switch. In a high speed packet switching system, it appears desirable to have a maximum per-switch delay in the

neighborhood of a few milliseconds. This means that the amount of buffering per link is a few hundred kilobits (assuming 100 Mb/s link speeds), not an unreasonable amount to provide on a per-link basis. A detailed evaluation of the cost and advantages of shared buffering remains to be done.

### **Partial Sorting**

The Starlite system suggests a possible improvement to the BPN fabric design. The routing network used in the Starlite design is a form of binary routing network (specifically, a banyan network) that will pass a sorted sequence of packets without conflict. It will also pass without conflict, a set of input packets that arrive on an input port with the same port number as their destination.

Suppose we replace the distribution network in the BPN fabric with a network that routes packets whenever it can do so without delaying them, and distributes packets otherwise. Intuitively, such a network appears likely to present the routing network with a better traffic pattern than is obtained by simply randomizing the traffic; this could lead to substantially higher throughputs. We plan to examine such a strategy in detail in the next few months and quantify the resulting performance advantage.

### 2.3. Design of Large Systems

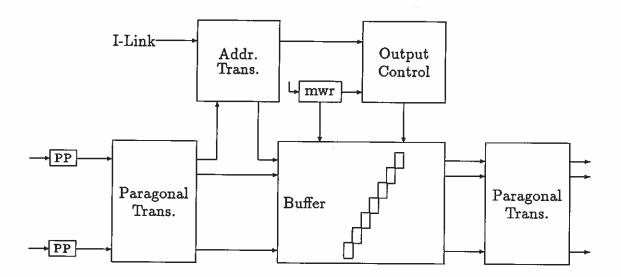

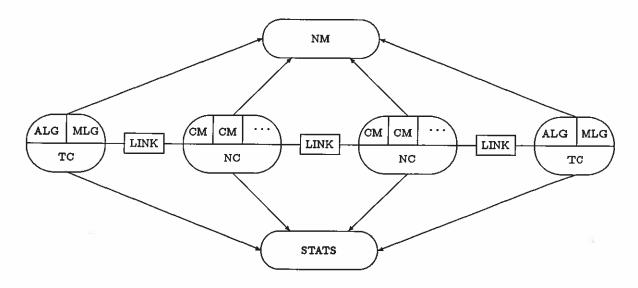

The BPN switch module has been designed as a component that can be used to construct the large switching systems required for supporting ubiquitous public networks. We have formulated a possible design for a local switching system, in order to obtain a better idea of the scale of the system and the associated control issues.

The proposed design supports up to 65,000 access lines and 4096 trunks, and is based on a hypothetical traffic mix<sup>1</sup> including 200 entertainment video sources, video telephones with an effective bandwidth of 8 Mb/s and busy 20% of the time, plus other traffic that is equivalent to the video telephone traffic in total resource requirements. For the broadcast video, it is assumed that a 90:10 rule applies; that is, in any group of users, 90% will be accessing 10% of the available channels. This, along with the assumptions on video phone traffic were used to select concentration ratios.

<sup>&</sup>lt;sup>1</sup>It should be noted, that this is purely hypothetical and not supported by any detailed traffic projections. The purpose is just to present a rough picture of a possible traffic mix, and how one might configure a system to support it.

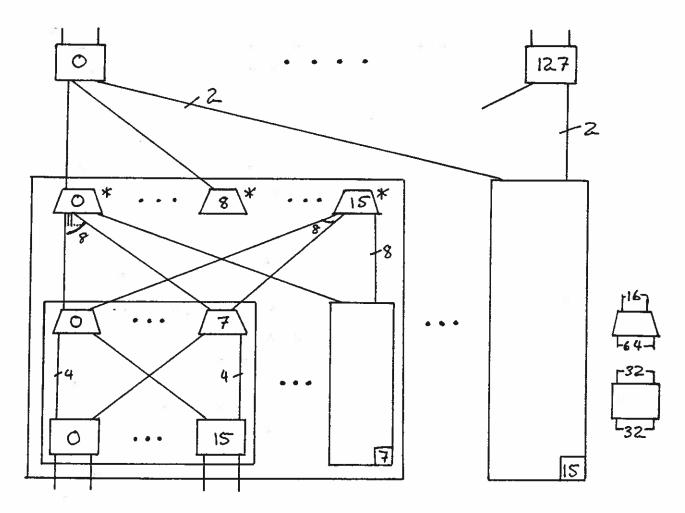

Figure 2.5: Local Switch Design

A block diagram of the system appears in Figure 2.5. The lines terminate at the bottom of the figure, trunks connect at the top. It is constructed from two types of switch modules, one with 64 links and the other with 80, and providing 4:1 concentration. The system has 128 back-end switch modules that connect to 4096 trunks and provide access to 16 major groups, which terminate 4096 lines each. The major groups each contain 16 back-end switch modules and 8 minor groups, terminating 512 lines each. The minor groups each contain 8 back-end switch modules and 16 front-end switch modules.

The hardware complexity of this system can be estimated based on the assumption that one unduplicated switch module can be implemented on 8-12 printed circuit boards. If the front-end switch modules in the minor groups are unduplicated and everything else is duplicated, a minor group requires two equipment frames, a major group requires 18 frames and the complete switch requires 304 frames. This

is roughly comparable in complexity to a telephone central office supporting the same number of lines.

This design raises several questions. First, one might ask, why structure the system in this way in the first place? Why not instead, simply scale the switch module to a much larger size? This turns out to be impractical for a variety of reasons, including expandability, timing, reliability and control partitioning. A large system of this sort must be broken down into a large number of fairly small, independent modules. This raises an interesting point with respect to the Starlite and Prelude switch fabrics. Those fabrics, like the BPN fabric, are useful mainly for constructing switch modules of moderate size; to build very large systems they must be configured together into a larger structure. In that context, many of the apparent distinctions among the different approaches become less significant.

Another question that arises is how connection management is handled in a large system. The simplest method conceptually is to allow the connection processors in each switch module to operate independently. While this can be workable, it requires more effort and more delay in the connection establishment process than is strictly necessary. It is possible to speed up the process considerably by using datagram routing within the switch, limiting the logical channel-based routing to the external lines and trunks. The regularity of the interconnection topology makes the implementation of datagram routing straight-forward for point-to-point connections. It remains unclear whether such an approach is practical for multipoint connections as well.

Using datagram routing on the inter-module links eliminates the need for most internal resource allocation, but still leaves the problem of resource allocation on the external links. To manage this, a database is required that tracks the status of the external links. We plan to explore the issue of how such a database should be organized to provide rapid access by the connection processors, that must use the information in the database to make routing decisions.

### Summary

Studies of switching architectures have and will continue to play an important role in our work on high speed packet switching. In the last year we have made some comparative studies of switch architectures and attempted to apply the lessons learned from these studies to improve the broadcast packet switch design. In the coming year, we expect to broaden this kind of study, to consider a wider range of alternative architectures. We also want to develop quantitative comparisons, as opposed to the qualitative comparisons made here.

# 3. Performance Studies

Faculty Research Associate

Jonathan Turner Riccardo Melen

The evaluation of any switching system architecture is determined in large part by performance issues. We have addressed performance issues in several different ways. Previous progress reports have reported on extensive simulation studies examining several aspects of the performance of the proposed Broadcast Packet Switch fabric. In this report, we examine two broader performance issues. First, we consider a general method of evaluating the loading characteristics of packet switching fabrics that dynamically distribute their load across all available paths. As we shall see, such fabrics can be made robust in the face of arbitrary traffic patterns with minimum complexity. We refer to the analysis method as fluid flow loading analysis, and using it, we derive several fundamental results for both pointto-point and multipoint packet switching fabrics. In section 3.2, we consider a class of fabrics in which all packets belonging to a particular connection are constrained to follow the same path. The prime motivation for making such a constraint is to eliminate the possibility of packet mis-ordering. As we shall see, this consideration leads to a natural generalization of the classical theory of non-blocking networks; in this report we define that generalization, outline the important problems and present a few fundamental results. We close this chapter with a brief description of simulation results which quantify the potential for packet misordering in the proposed broadcast packet switch design. These results are intended to to be used to help design a mechanism to resequence misordered packets on a switch module basis.

### 3.1. Fluid Flow Loading Analysis

In this section we introduce a systematic method of analyzing the effects of a given traffic configuration on packet switching fabrics that dynamically distribute

load across all available paths, and apply it to the analysis of several proposed architectures. Our method allows us to prove theorems characterizing the worst-case loading for various switching fabrics. The section gives several such theorems, both as illustrations of our method and for their inherent interest. Proofs are omitted for brevity; readers are referred to ?? for further details.

We note that the method is fairly easy to apply and leads to useful insights that can guide the switching system architect to better designs. It is not a complete characterization, as it ignores queueing and contention, but when used in conjunction with queueing and simulation models based on uniform random traffic, it can provide the designer and performance analyst with a more complete understanding of system performance.

### **Networks for Point-to-Point Communication**

We define a packet switching network (or simply network) as a directed graph G = (N, L) consisting of a set of nodes N and a set of directed arcs or links L. In addition, G contains a set of distinguished input nodes I and a set of distinguished output nodes O. Input and output nodes are also referred to as ports. Each input port has a single outgoing link and no incoming links, while each output port contains a single incoming link and no outgoing links.

We limit ourselves to networks in which the number of input nodes equals the number of output nodes. When we refer to an n port network, we mean a network with n input nodes and n output nodes, numbered from 0 to n-1. We also limit ourselves to networks, which can be divided into a sequence of stages. We say that input ports are in stage 0 and for i > 0, a node v is in stage i if for all links (u, v), u is in stage i-1. A link (u, v) is said to be in stage i if u is in stage i. In the networks we consider, all output ports are in a separate stage by themselves. When we refer to a k stage network, we mean that there are k stages containing internal nodes; that is, we neglect the input and output stages.