# A GIGABIT LOCAL ATM TESTBED FOR MULTIMEDIA APPLICATIONS

## System Architecture Document for GIGABIT SWITCHING TECHNOLOGY

Version 3.5

Technical Report ARL-94-11 August 27, 1998

> **by:** Jonathan S. Turner ARL Staff ANG Staff

**Document prepared by:**

Zubin D. Dittia J. Andrew Fingerhut

**Department of Computer Science**

| 1 INTRODUCTION                                                 | 4  |

|----------------------------------------------------------------|----|

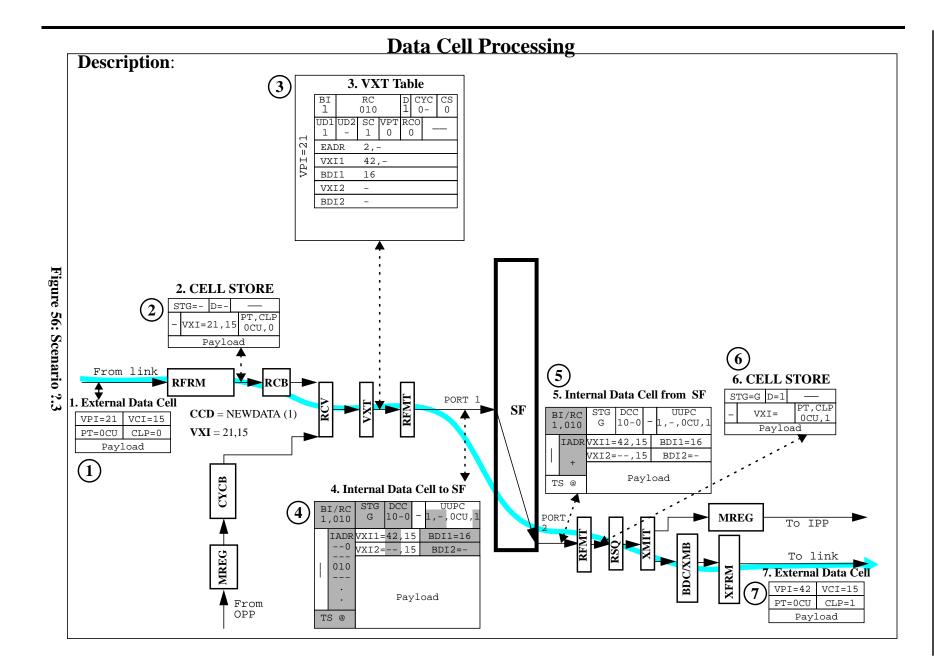

| 2 OVERVIEW OF THE ARPA PROJECT                                 | 4  |

| 3 SWITCH DESIGN                                                | 5  |

| 3.1 Introduction                                               | 5  |

| 3.2 Basic Operation                                            | 7  |

| 3.3 Resequencing Options                                       | 11 |

| 3.4 Configuring the Network to Avoid Blocking                  | 13 |

| 4 PROTOTYPE SWITCH CONFIGURATION                               | 13 |

| 5 TESTBED OVERVIEW                                             | 15 |

| 6 CELL FORMATS                                                 | 15 |

| 6.1 External Data Cell Format                                  |    |

| 6.2 I/O and Recycling Data Cell Format                         | 19 |

| 6.3 Internal Data Cell Format                                  | 20 |

| 6.4 Control Cell Format                                        |    |

| 7 CONTROL TABLES AND REGISTERS                                 | 29 |

| 7.1 Virtual Path/Circuit Translation Tables                    | 30 |

| 7.2 Maintenance Registers                                      | 32 |

| 7.2.1 IPP Maintenance Register Fields                          | 32 |

| 7.2.2 OPP Maintenance Register Fields                          | 39 |

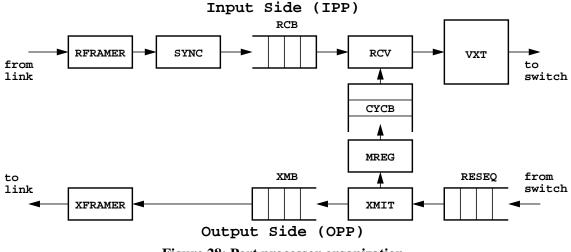

| 8 PORT PROCESSOR DESIGN                                        | 45 |

| 8.1 Overview                                                   | 45 |

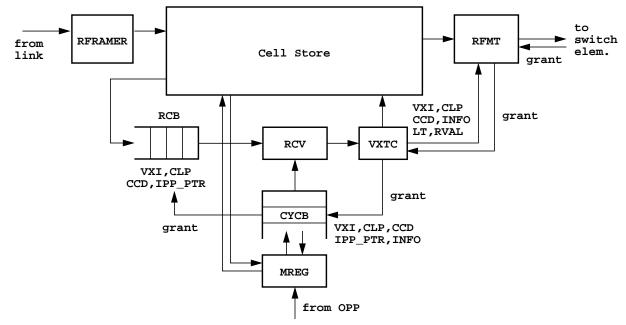

| 8.2 Input Port Processor Design                                | 47 |

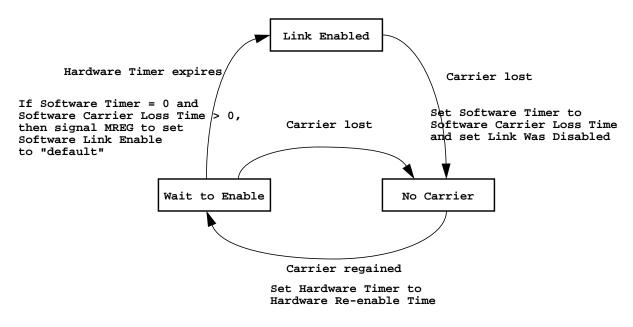

| 8.2.1 Link Enabling and Disabling Circuitry                    | 48 |

| 8.2.2 Receive Framer (rframer)                                 | 50 |

| 8.2.3 Cell Store (cstr)                                        | 51 |

| 8.2.4 Receive Buffer (rcb)                                     | 51 |

| 8.2.5 Maintenance Register (mreg)                              | 52 |

| 8.2.6 Recycling Buffer (cycb)                                  | 53 |

| 8.2.7 Receive Circuit (rcv)                                    | 54 |

| 8.2.8 Virtual Circuit Translation Table Control Circuit (vxtc) | 55 |

| 8.2.9 Virtual Circuit Translation Table (vxt)                  | 56 |

| 8.2.10 Reformatter (rfmt)                                      | 56 |

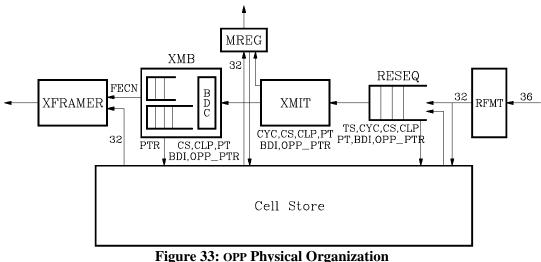

| 8.3 Output Port Processor Design                               | 59 |

| 8.3.1 Reformatter (rfmt)                                       | 59 |

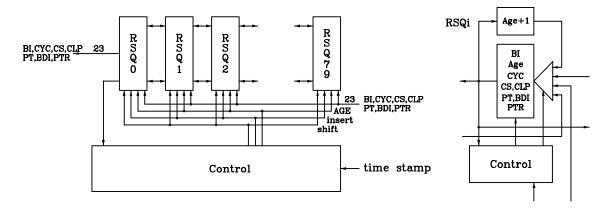

| 8.3.2 Resequencer (reseq)                                      | 61 |

| 8.3.3 Transmit Circuit (xmit)                                  | 62 |

| 8.3.4 Maintenance Register (mreg)                              | 62 |

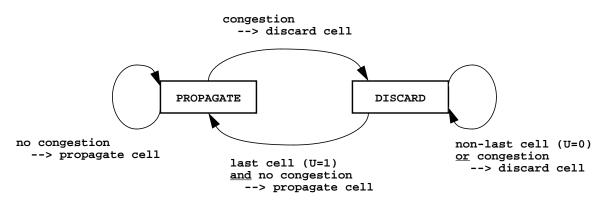

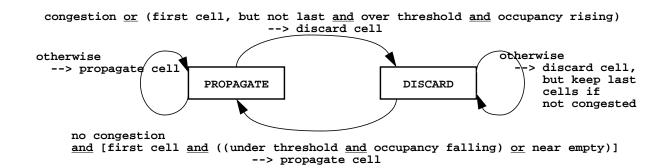

| 8.3.5 Block Discard Controller (bdc)                           | 63 |

| 8.3.6 Transmit Buffer (xmb)                                    | 67 |

| 8.3.7 Transmit Framer (xframer)                                | 68 |

| 8.3.8 Cell Store (cstr)                                        |    |

| 9 SWITCH ELEMENT DESIGN                                        | 68 |

| 9.1 Data Paths and Grants                                      | 69 |

| 9.2 Behavior of Switching Fabric                               | 69 |

| 9.3 Switch Element Interconnection and Option Pins             | 70 |

| 9.4 Behavior of Switch Element Chips                           | 73 |

| 9.5 Behavior of Major Circuits in the Switch Element Chip74                                     |

|-------------------------------------------------------------------------------------------------|

| 9.5.1 Distribution Circuit (dstc)                                                               |

| 9.5.2 Input Crossbar and Grant Generation Circuit (ixbar, ggc)75                                |

| 9.5.3 Shared Buffer and Control Circuit                                                         |

| 9.5.4 Output Crossbar75                                                                         |

| 9.5.5 Header Modification Circuit (hmc)                                                         |

| 9.6 Parity Checking76                                                                           |

| 9.7 Deskewing the Signals Sent Between Chips76                                                  |

| 9.8 System Reset77                                                                              |

| 9.9 Other Signals Sent to All Chips                                                             |

| 10 OPERATIONAL SCENARIOS                                                                        |

| 10.1 Testing79                                                                                  |

| 10.2 Setting Up, Modifying, and Removing Connections                                            |

| 10.2.1 Setting up a point to point connection                                                   |

| 10.2.2 Adding endpoints to create a point to multipoint connection83                            |

| 10.2.3 Removing endpoints from a point to multipoint connection, and transitional time stamping |

| 83                                                                                              |

| 10.2.4 Removing a point to point connection                                                     |

| 10.2.5 Multipoint to Multipoint Connections                                                     |

| 10.3 Monitoring Statistics and Error Conditions                                                 |

| 10.4 Switch Reset and Initialization84                                                          |

| 11 Known Problems and Possibly Surprising Features                                              |

# **1 INTRODUCTION**

This document details the design specifications for a high speed multicast virtual circuit switch being developed at Washington University. A prototype implementation of this switching fabric forms an important component of a bigger project, whose goal is the investigation and development of two key gigabit technologies:

- · Multirate gigabit switching, and

- Host network interfacing for high bandwidth distributed and multimedia applications.

The project itself is funded by ARPA, and work related to the project is being done by faculty, staff, and students from the Applied Research Laboratory (ARL) and the Advanced Networks Group (ANG), both of which are groups in the Department of Computer Science at Washington University.

The innovative aspects of the switch architecture described in this document include: a novel cell recycling architecture, a nonblocking design that is asymptotically optimal in both the switching network complexity and in the amount of memory required for multicast address translation, which supports fast (constant time) addition and deletion of endpoints to a multicast connection. As one of the ARPA project deliverables, three prototype switches built using this design will be used to form a local ATM test bed that will interconnect a number of workstations. The primary purpose of this report is to serve as a comprehensive and detailed reference guide for hardware and software engineers working to put together both the prototype switch and the LAN test bed. Other interested parties may also find parts of the document useful for reference purposes, or for an overview of the project.

This document has been structured so as to allow for clarity as well as completeness. A top-down approach has been chosen for presentation, with initial sections of the document giving a broad overview of the ARPA project, the switch design, and the test bed overview, while later sections focus on detailed descriptions and implementation specifics for various functional units.

The material outlined in this document is the result of a series of meetings jointly organized by ARL and ANG with a view to arriving at a complete specification of the system architecture. It is possible that some of the ideas or designs presented here may change over time, as the prototype implementations take shape, and as more experience is acquired. It is anticipated that the document will evolve in parallel with work on the project, so readers wanting to use it for reference should acquire the latest version of the document.

## **2 OVERVIEW OF THE ARPA PROJECT**

The gigabit switching technology that will be used is based on a novel nonblocking cell-recycling architecture. An important aspect of this architecture is that it provides extremely efficient support for multicast, which is crucial for a number of key applications, including teleconferencing, multiparticipant collaboration, distributed computing, video distribution, etc. The architecture is optimal in switching network complexity, memory requirements for multicast address translation, and in the amount of effort required for multicast connection modification. Furthermore, it is capable of supporting multirate access between the network and hosts. In particular, it will support link rates of 155 Mbps, 620 Mbps, 1.2 Gbps, and 2.4 Gbps. The external cell format follows the ATM standard. The switching system can easily be used in both LAN and WAN environments with minimum modification.

The host network interface that will be developed uses an ATM interconnect within the host to serve as the high speed equivalent of an I/O bus. The interconnect itself has a daisy-chained topology, and is constructed using a number of ATM port interconnect controllers (APICs), each of which interfaces to one or more devices within the host. The interface design will allow sustained data transfer rates of up to 1.2 Gbps to various devices within the host, including display, memory, disk, etc. One of the design objectives is to provide easy and efficient interfacing to different host platforms and devices. This will ensure that minimum modifications to the operating system will be required, and both existing and new network protocols can be used.

The project has been divided into five tasks:

- 1. Designing and prototyping of the recycling switch fabric and its port processors and link interfaces.

- 2. Development of signalling software for use with the switch; this will include signalling for the user-network interface, as well as signalling between entities within the network.

- 3. Design and prototyping of the ATM port interconnect controller (APIC), and interfacing it to the host memory and the workstation display.

- 4. Extending the operating system to incorporate device drivers for managing devices with back end interfaces to the ATM interconnect, and modifications to the TCP/IP protocol implementation to allow high speed but transparent operation over the new host network interface.

- 5. Creation of an ATM LAN test bed comprising three switches, and a number of multimedia workstations and multimedia file (image and/or document) servers.

- 6. Development of example applications and experimental studies. This will include using an n-body benchmark application and a multiparticipant collaborative application to investigate hardware and application performance issues.

As mentioned earlier, our primary concern in this document is with the first task, viz., design and prototyping of the switch fabric and related chips. The overall project is slated for completion in 1996, but most of the work related to task 1 has to be completed by the end of 1995.

# **3 SWITCH DESIGN**

### 3.1 Introduction

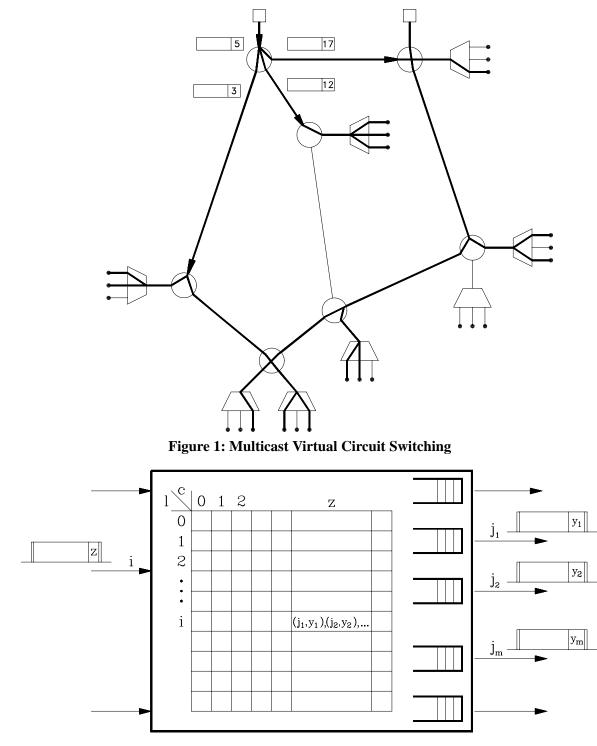

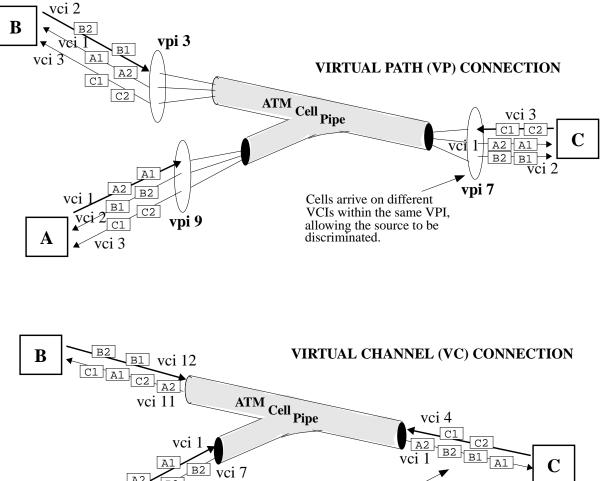

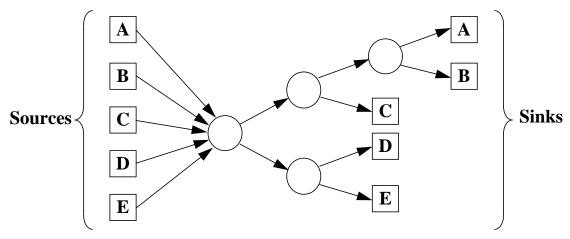

Multicast virtual circuit networks support communication paths from a sender to an arbitrary number of receivers, as illustrated in Figure 1. As shown, multicast virtual circuits induce a tree in a network connecting a sender to one or more receivers. Switching systems participating in the virtual circuit replicate received cells, using *virtual circuit identifiers* in the cell headers to access control information stored in the switching system's internal control tables. This information is then used to identify the outputs to which the cells should be sent and to relabel the copies before forwarding them on to other switching systems.

Figure 2 illustrates the function of a multicast virtual circuit switch in more detail. The switch includes control information, shown here as a table, which for each incoming virtual circuit provides a list of outputs and outgoing virtual circuit identifiers. For a cell received on input link *i* and virtual circuit *z*, the switch forwards copies to outputs  $j_1$ ,  $j_2$ , ... after relabeling them with new virtual circuit identifiers,  $y_1, y_2, ...$  Notice that if the switch has *n* inputs and outputs and outputs and each output supports up to *m* virtual circuits, one can describe any collection of multicast virtual circuits with *mn* words of memory. One simply provides for each (output,VCI) pair, the identity of the (input,VCI) pair from which it is to receive cells. Unfortunately, this method of defining a set of multicast connections is not particularly helpful in switching, as it does not give one an efficient way to map (input,VCI) pairs to the desired list of (output,VCI) pairs. Existing virtual circuit switch architectures describe multicast virtual circuits in different ways, which while suitable for switching, use far more than mn words of memory. The broadcast packet switch [Turner-88b,Turner-88c], for example, requires  $mn^2/2$  words of memory under worst-case conditions. Moreover, the time required to update a multicast connection grows with the size of the connection. Other architectures require even greater amounts of memory. For example, Lee's multicast switching system [Lee-88] requires  $mn^3/2$  words of memory under worst-case conditions.

The multicast switch architecture described here has  $O(n \log n)$  hardware complexity and it is nonblocking, in the sense that it is always possible to accommodate a new multicast connection or augment an existing one, so long as the required bandwidth is available at the external links. It requires less than 2mn words of memory for multicast

#### **Figure 2: Multicast Switch Functionality**

address translation. Moreover, the overhead for establishing or modifying a multicast connection is independent of the size of the connection or the switching network.

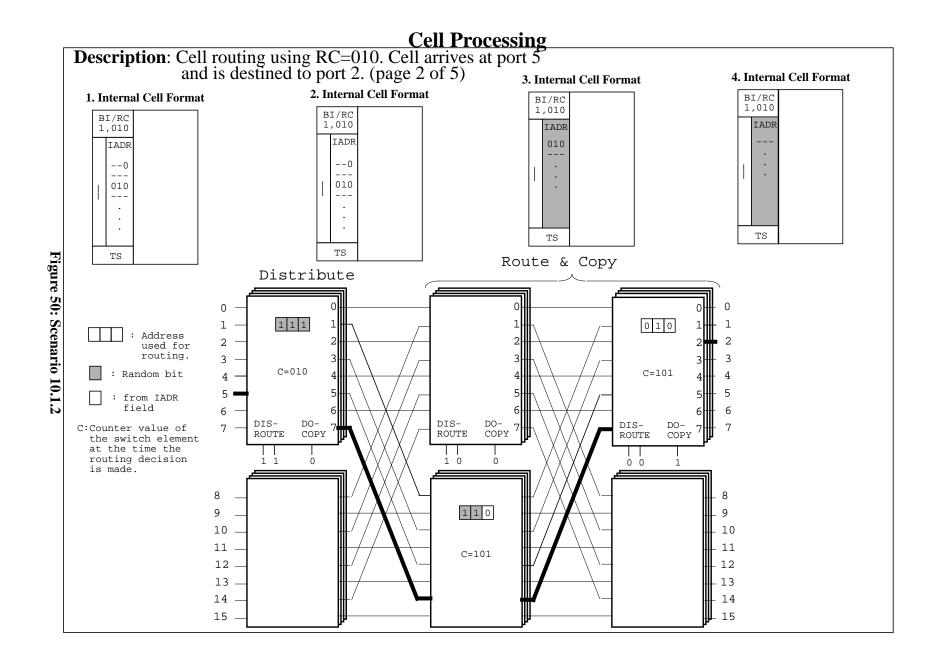

### 3.2 Basic Operation

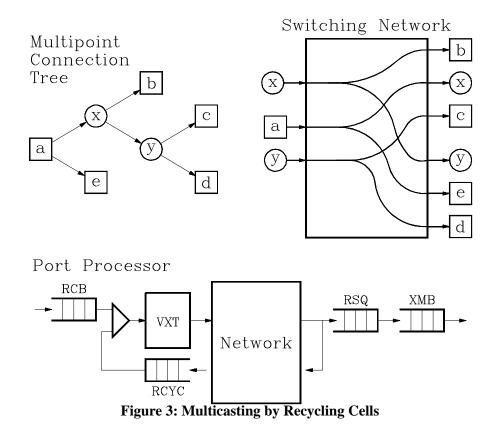

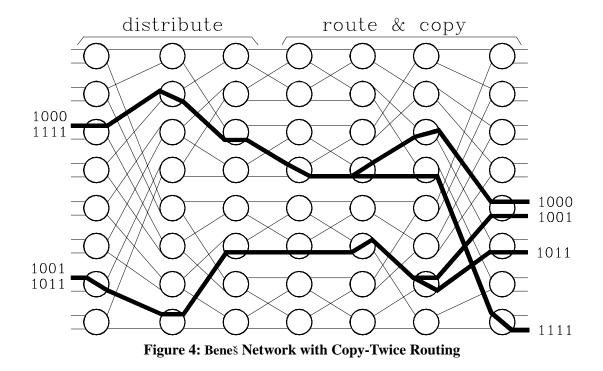

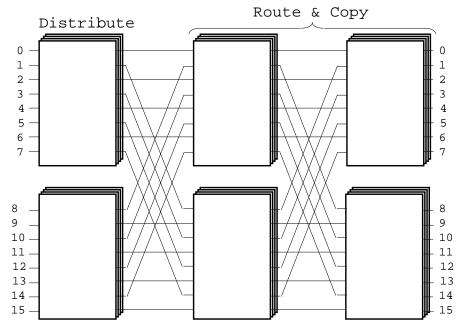

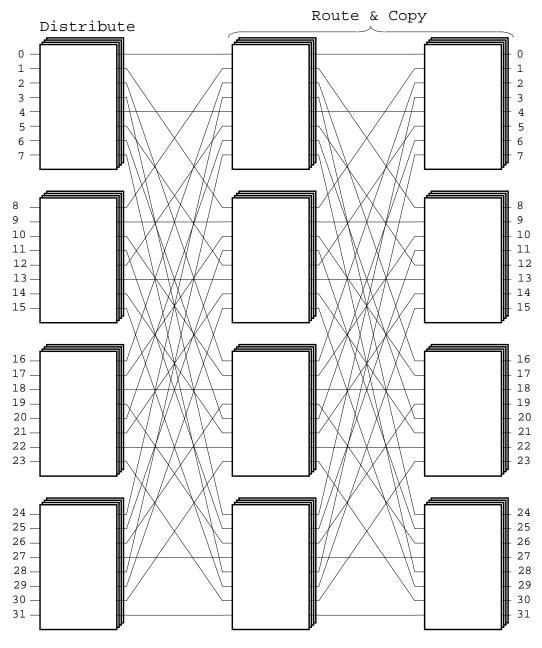

The basic principle behind the recycling architecture is illustrated in Figure 3. To implement a multicast connection, a binary tree is constructed with the source switch port at its root and the destination switch ports at its leaves. Internal nodes represent switch ports acting as relay points, which accept cells from the switch, but then recycle them back into the switch after relabeling the cells with a new destination pair identifying the next two switch ports to which they should be sent. There are many possibilities for constructing the switching network. A Beneš network, in which the switches in the first half of the network distribute cells randomly in order to balance the load evenly, and in which local buffers are used to resolve contention, provides the lowest cost solution known. Figure 4 illustrates a 16 port network of binary switch elements in which two cells with two destinations each are forwarded from inputs to outputs. Note that cells are copied at the latest possible point in the network and this point is easily determined by bit-wise consideration of the destination addresses. This scheme can easily be extended to networks constructed from larger switch elements. It can be shown that given any collection of virtual circuits, the load placed on any of the switching network's internal links is at most equal to the load on the most heavily loaded external port. In other words, there is no collection of virtual circuits that can be handled by the external links that cannot also be handled by the network. That is, this network is nonblocking. Other switching networks, suitably extended to provide the copy-by-two function, can also be used in the recycling architecture.

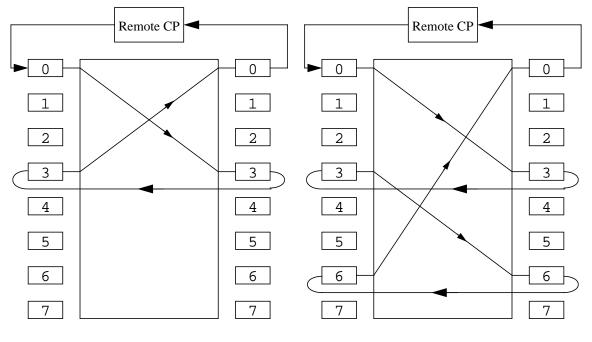

The lower part of Figure 3 details the hardware associated with each port of the switching system. The resequencer is responsible for restoring proper ordering of cells on output from the network, and also to ensure that additions or deletions of endpoints to multicast connections do not change the proper cell ordering. The resequencing buffer is labeled RSQ in Figure 3. Given a virtual circuit identifier, obtained from a cell's header, the *Virtual Circuit Translation Table* (VXT) provides two (output,VCI) pairs that are added to the cell header plus two additional bits that indicate, for each pair, whether it is to be recirculated another time, or not. The *Receive Buffer* (RCB) holds cells that are waiting to enter the switching network, while the *Transmit Buffer* (XMB) holds cells waiting to be transmitted on the outgoing link.

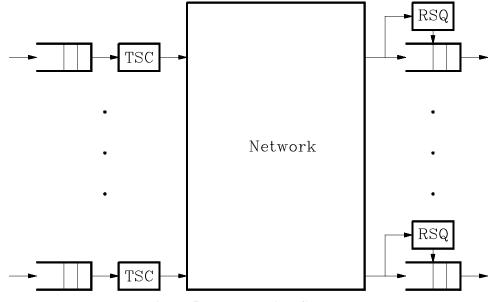

Figure 5 illustrates the resequencing operation. Cells entering the network pass through a Time Stamp Circuit

#### **Figure 5: Resequencing Concept**

(TSC), which records the time the cell enters the network in its header (the TSCs are all driven from a common clock). On output, the cell is placed in a resequencing buffer which is managed by a *Resequencing Buffer Controller* (RBC). When a cell leaves the switch and enters the resequencing buffer, the RBC computes its age from the time of entry and the current time. It also keeps track of the age of all cells stored in the buffer and allows cells to leave the buffer in oldest-first order. If the oldest cell is not "old enough", no cell is output. The purpose of this is to allow cells that require an unusually long time to pass through the switching network to catch up with cells that have already reached the output buffer.

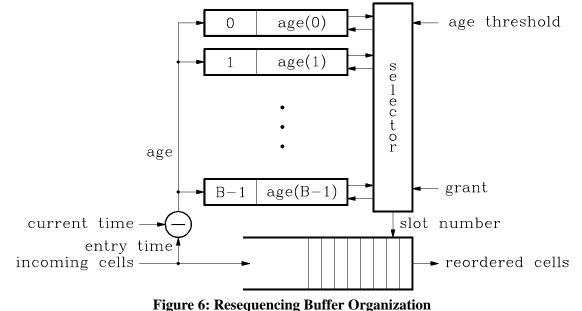

Figure 6 shows the organization of the resequencing buffer and buffer controller. The buffer is organized as

a set of slots, with each slot being big enough to hold a single ATM cell. The controller is organized similarly, with a

*control slot* for each buffer slot. Each control slot contains two pieces of information, a *slot number* which specifies the buffer slot it is associated with and the age of the cell (if any) stored in that slot. The *selector*, at the right, selects the oldest cell during output operations, compares that cell's age to a given age threshold, and if appropriate, forwards the cell's slot number to the buffer which then forwards the cell to the downstream circuitry. The *grant* signal is asserted by the downstream circuit if it is prepared to receive a cell; this provides a simple form of flow control. During input operations, the selector selects any idle control slot, inserts the age of the arriving cell into that slot, and passes the slot number to the buffer, which places the arriving cell in the specified slot. We analyze the resequencer depth requirements in Section 3.3.

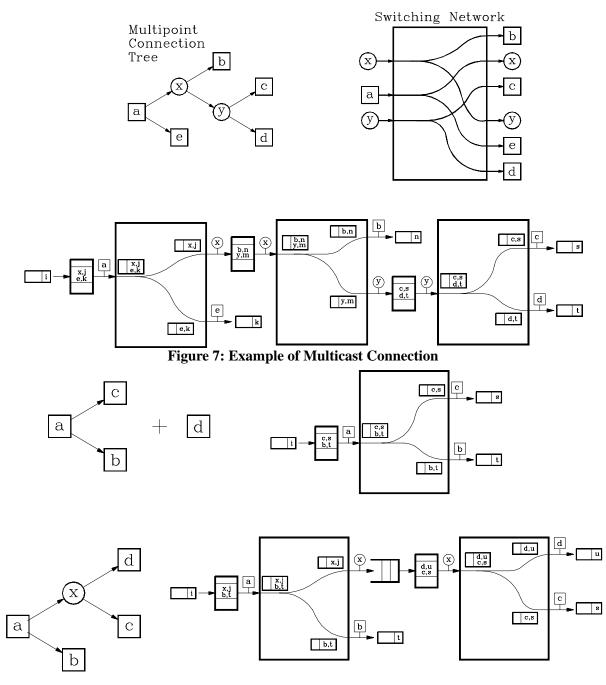

Figure 7 illustrates the operation of the multicast switch in more detail. In this example, a multicast connection delivers cells from input *a* to outputs *b*, *c*, *d* and *e*, using ports *x* and *y* as relay points. In the lower part of the diagram, the implementation of the connection is shown in an 'unrolled' form, to clarify the flow of cells through the system. It should be understood however, that this is purely illustrative. There is in fact just one switching network, not three, and cells are simply sent through it multiple times in order to reach all the destinations. In the example, cells entering at input *a* with VCI *i*, are forwarded to output *e*, VCI *k* and output *x*, VCI *j*. At *x*, the cell is recycled, with VCI *j* used to select a new table entry from *x*'s VXT. The resulting information causes the cell to be forwarded to output *b*, VCI *n* and output *y*, VCI *m*. At *y*, the cell is recycled again, with the resulting copies delivered to *c* and *d*. Although it is not shown in the figure, the table entries contain one bit for each copy, indicating whether that copy should recycle or go out to the link.

We can also construct multicast connections to which multiple input ports can send cells. One simply sets up the virtual circuit tables of each of the source input ports so that they forward cells to the port at the root of the tree, which then recycles them along the tree. Of course, the total traffic from all the source ports must be limited to the total bandwidth allocated to the connection. In a connection where a port is both a source and a destination, we often do not want to send to a source a copy of a cell that it sent in the first place (although we do want the other participants to receive it). This is easily accomplished by including the identity of the original source port in the cell and checking this at the destination in order to discard unwanted copies.

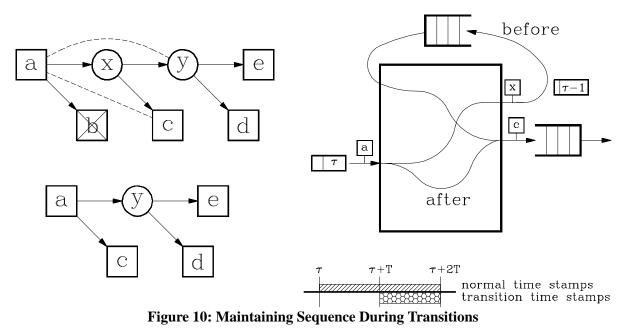

To add an endpoint to a multicast connection, some rearrangement of the connection is needed. This is illustrated in Figure 8. Let d be the output that is to be added to a connection, let c be an output closest to the root of the

tree and let a be its parent. Select a switch port x with a minimum amount of recycling traffic. Enter c and d in an unused VXT entry at x and then replace c with x in a's VXT entry. These changes have the effect of inserting x into the tree, with children c and d, as illustrated in the figure.

Dropping an endpoint is similar, as illustrated in Figure 9. Let c be the output to be removed from a connection and let d be its sibling in the tree, x be its parent and a its grandparent. In a's VXT entry, replace x with d. If the output to be removed has no grandparent but its sibling has children, replace the parent's VXT entry with the sibling's children. For example, in Figure 9, if b were the output to be deleted, we would copy x's VXT entry to a, effectively removing x from the connection. If the output to be removed has no grandparent and its sibling has no children, then we simply drop the output to be removed from its parent's VXT entry, and the connection reverts to a simple point-to-

#### **Figure 9: Dropping an Endpoint**

point connection. For example, in the bottom part of Figure 9, if b were to be dropped from this connection, we would be left with the point-to-point connection from a to d.

### **3.3 Resequencing Options**

There are two main options for resequencing in the recycling architecture. We could either resequence cells after every pass through the fabric (this is our preferred approach for the prototype design), or we could do the resequencing only after the last pass i.e., when cells are ready to leave the switch. We consider first this latter option. When we resequence only in the last pass, the resequencing buffer must be dimensioned to delay cells long enough so that slow cells have a chance to catch up with fast cells. That is, the resequencing buffer must be at least as large as the largest variation expected in the delay of cells through the system, when they recycle the maximum number of times. Since, both the total delay and the delay variation can change over time, the most practical approach appears to be to dimension the buffer to be equal to the maximum delay that would be expected under the heaviest loading conditions.

A naive analysis reveals how the delay grows with *n*, the number of inputs and outputs to the system. Let  $\mu_t$  and  $\sigma_t$  be the mean and standard deviation of the delay in each stage of the switching network. Let  $\mu_t$  and  $\sigma_t$  be the mean and standard deviation for cells passing through the network the maximum number of times. Let *r* be the number of stages of switching that these cells pass through, altogether. Then  $\mu_t = r\mu$ , and if the delays in each stage are independent (often a reasonable approximation), then  $\sigma_t = \sqrt{r\sigma}$ . A reasonable engineering rule is to select the resequencer depth equal to the mean delay plus some number *h* of standard deviations past the mean. This gives a resequencer depth of  $\mu_t + h\sigma_t = r\mu + h\sqrt{r\sigma}$ . Consequently, the depth grows in proportion to *r* and for a Beneš network,  $r = (2\log_d n - 1)\log_2 F$ , where *F* is the maximum fanout. For d = 2 and F = n, this is too much if we are to obtain an overall system cost that grows in proportion to  $n\log n$ .

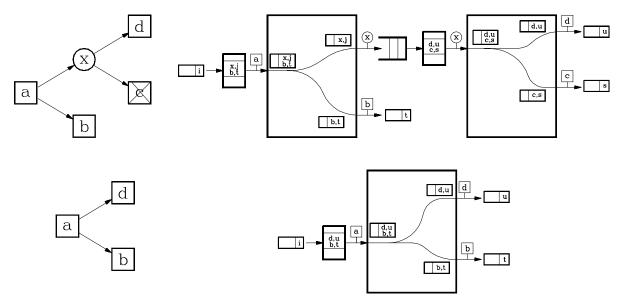

If we follow the other approach of resequencing cells after every pass rather than waiting until the cells exit, it can be shown that it is possible to obtain the desired complexity. This raises a new issue however, in that when we modify a connection, we potentially change the depth of the tree. This means that cells take a different number of passes through the network and introduces the possibility of cells getting out of sequence (even though they are correctly sequenced on each pass). When an endpoint is added to a connection its new sibling becomes repositioned in the tree and its cells experience a longer delay, because of the additional pass through the network. Consequently, there is a momentary gap in the flow of cells to the output, but the ordering of the cells is unaffected. However, when an endpoint is removed from a connection, outputs immediately following the *cut point*, are moved closer to the root of the tree

and so the cells being sent to them experience a shorter delay and are at risk of being mis-sequenced with cells that left the cut point just before the change.

To prevent cells from being delivered out of order, the resequencer must provide an extra delay for cells forwarded immediately after the cut occurs. Let *T* be the maximum delay we expect to see in one pass through the network (equal to  $(2(\log_d n) - 1)\mu + \sqrt{2(\log_d n) - 1}h\sigma$  for the Beneš network). Let  $\tau$  be the moment when the VXT at the cut point is changed and let *R* be a new register included in the time-stamping circuit of every input port processor. Assume the clock used for time stamping is incremented once for every operational cycle of the system (one cell time) and assume also that the time stamp field of the cell and the register *R* include an extra low order bit that can be used to represent a "half-step." Normally, cells are time stamped with the current time value. We modify this process for the affected virtual circuit in the time period immediately following the change in the following way. At time  $\tau$ , the register *R* is set equal to  $\tau + T$ . After that time, cells in the affected virtual circuit are time stamped with either the current time or the value of *R*, whichever is larger. If *R* is chosen, we also add 1/2 to *R*. This process compresses the time stamps in the period of length 2*T* following the transition into the time period [ $\tau + T$ ,  $\tau + 2T$ ] (see Figure 10). This ensures that cells immediately following the transition are delayed for an extra time period in the resequencer, giving cells that entered just before the transition time to catch up and get placed in the proper sequence. The time stamping process returns to normal no later than 2*T* cycles following the transition. A consequence of this is that two consecutive deletions of endpoints should be separated by at least 2*T* cycles.

These same ideas can be generalized to allow resequencing after every p passes for some p. Letting  $z = (2\log_d n) - 1$  and F be the maximum fanout, we obtain a resequencer depth of

$$\mu z(1+p) + (1+\sqrt{p})h\sigma\sqrt{z}$$

and a maximum delay of

$$\mu z \lg F + h \sigma \sqrt{z} (\lg F) / \sqrt{p}$$

The table in Figure 11 compares per pass resequencing (p=1) to the case where we resequence only on exit  $(p = \lg F)$  when  $\mu = 3$ ,  $\sigma = 2$ , h = 10 and F = n. In the table, *r* is the number of stages in a worst-case path. The expression given in the column labeled multipass gives the depth and delay (in cell times) for the resequence-on-exit case. For the largest system, the per pass resequencing delay is 1184 cell times, or under 700 µs for a system configured to support external link speeds of 620 Mb/s. To put things in perspective, this is less than the delay in many existing digital tele-

|      |     | <i>_</i>   | per p | ass reseq | multipass                |  |  |

|------|-----|------------|-------|-----------|--------------------------|--|--|

| n    | r   | $\sqrt{r}$ | depth | max delay | $r\mu + h\sqrt{r\sigma}$ |  |  |

| 8    | 3   | 1.4        | 46    | 69        | 9 + 28 = 37              |  |  |

| 64   | 18  | 4.2        | 88    | 264       | 54 + 84 = 138            |  |  |

| 512  | 45  | 6.7        | 120   | 540       | 135 + 134 = 269          |  |  |

| 4096 | 84  | 9.2        | 148   | 888       | 252 + 184 = 436          |  |  |

| 32K  | 135 | 11.6       | 174   | 1305      | 405 + 232 = 637          |  |  |

Figure 11: Comparison of Per Pass Resequencing and Resequence on Exit

phone switches, so even the largest value in the table is quite reasonable. The resequencer depth in the largest case is getting fairly large, although it's arguably still acceptable, since the transmit buffer of the output port is likely to be at least as large. We'll introduce mechanisms in the next section which can improve both of these cases, but the point to be made here is that even without further refinements, excellent performance is possible. For the purposes of the prototype switch, we use a resequencer depth of 80 cell slots. This ensures that the probability of mis-sequenced cells appearing on an output link is vanishingly small.

### 3.4 Configuring the Network to Avoid Blocking

The recycling architecture can be configured so that it never blocks a new connection request if the network's internal bandwidth is sufficiently higher than the total bandwidth of the external links. It can be shown that the necessary *speed advantage* is modest, making the recycling architecture practically useful.

In the following discussion, we use normalized bandwidths; this normalization is achieved by defining the bandwidth of one of the switch's internal data paths to be 1, and expressing all other bandwidths relative to this. Let  $\gamma$  be the total bandwidth of the external links, and let *B* be the maximum data rate for any single connection. Also, let *n* be the number of inputs and outputs of the network. Then it can be shown [Turner-93a] that if  $2\gamma/n + B \le 1$ , a new connection can never block because of insufficient port bandwidth. Furthermore, if  $\delta$  is the fraction of exiting traffic that belongs to multipoint connections, it is sufficient to have  $(1 + \delta)\gamma/n + B \le 1$  to ensure nonblocking behavior. If we let  $B = c \gamma/n$  (i.e., B = c times the average link rate) then this condition holds when the speed advantage  $(n/\gamma)$  is greater than or equal to  $1 + \delta + c$ . So, when  $\delta = c = 1$  (the worst-case condition), we require a 3:1 speed advantage. If  $\delta = c = 1/2$ , a 2:1 speed advantage suffices. In the prototype design, we have chosen a speed advantage slightly larger than 2:1.

# **4 PROTOTYPE SWITCH CONFIGURATION**

The recycling architecture described in the previous section can be used to implement very large switching systems with a modest cost per port. In this section, we outline the design of such a system. The prototype switch will be built around this system; many of the later sections of this document focus on its design specifications in detail.

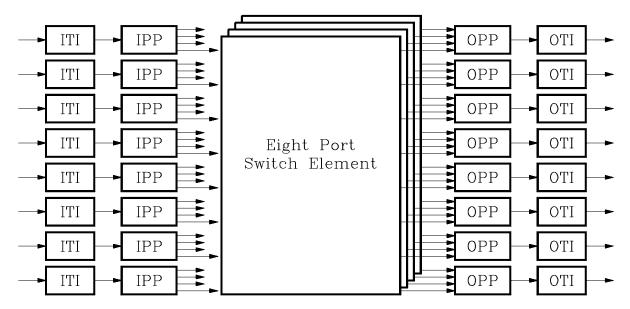

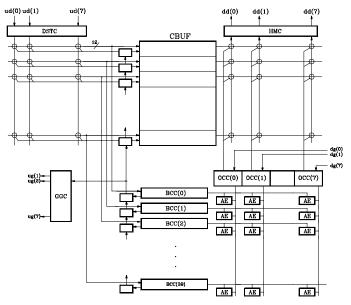

Figure 12 is a schematic of the configuration that will be used in the prototype switch. Because of clock speed limitations and the number of pins that a single chip may have, an  $8 \times 8$  switch element cannot be built on a single chip with current technology. Although a bit-sliced structure for the switch elements, with one control chip and *k* data chips for each switch element, would enable us to construct a switch element with more ports, we have chosen not to follow this approach for the prototype design. Instead, four identical chips operating in parallel implement one  $8 \times 8$  switch element. Each of the four chips receives one fourth of the data of each cell. Each chip also receives an identical copy

**Figure 12: Prototype Switch Configuration**

of the routing information for each cell. All four chips make identical routing choices simultaneously, so that the outputs of the four chips can be used to reconstruct the original cell. This choice was made to reduce the number of different chip types and the required design effort.

The input and output transmission interfaces (ITI and OTI in the figure) are responsible for interfacing to SO-NET at 155 Mbps or 620 Mbps, and to G-link at 1.2 or 2.4 Gbps. The switch itself is organized as a single eight port switch element, implemented with four identical chips operating in parallel. Each port of each chip has a 12-bit wide data paths (four of these are for control, and the remaining eight are data bits; the reason for using this 12-bit wide data path will become apparent later when we describe the internal cell formats). All four chips combined can support a data rate of 3.2 Gbps on each of the eight ports. This is 4/3 times the maximum data rate on a link (2.4 Gbps), thus providing a speed advantage. We seek to constrain the load on the switch ports to no more than 75% to minimize queueing delay and cell loss. For a 620 Mbps link, this leaves 3/4 of the switch bandwidth available for recycling. This scheme can easily be seen to apply for 1.2 Gbps links too; in this case, half of the switch bandwidth would be available for recycling.

The switch organization shown in the figure does not include a control processor. This is because the switch will be controlled remotely. Each port in the system can be optionally configured to send or receive control cells from a remote controlling process. These control cells can be used to access various control registers in the port processor chip, as well as modify the virtual circuit translation tables (VXTs), thus allowing for creation, deletion, and modification of connections. Since most of the connection setup delay is due to software in the control processor, the extra delay introduced by usage of a remote controlling process (rather than a local one) is insignificant.

The counterpart in the prototype design of the  $2 \times 2$  switch elements used in the Beneš network in Figure 4 is the single  $8 \times 8$  switch element comprising all of the four parallel switching planes shown in Figure 12. Each such plane of the switch element resides on a single chip, and internally consists of input and output crossbars with intermediate buffers. The copying occurs in the output crossbar. The motivating factor used to select this design for the switching element in preference to a single crossbar is the reduced circuitry that results on the chip.

Notice that for a switch with more than eight ports, multiple eight port switch elements would have to be interconnected in a fashion similar to the Beneš network in Figure 4. Although the design of the chips permit such interconnection, construction of such a larger switch is not part of the proposed prototype implementation.

**Figure 13: Planned Testbed Configuration**

## **5 TESTBED OVERVIEW**

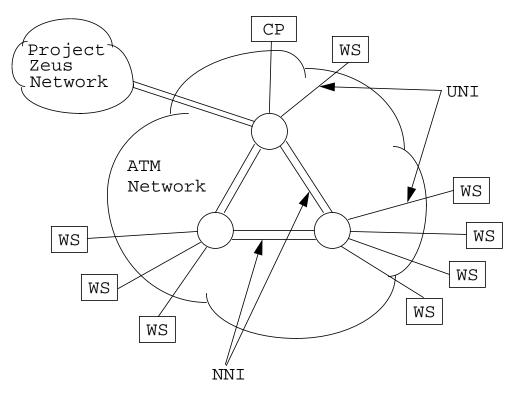

Figure 13 shows the configuration of the ATM LAN test bed that is to be constructed using three of the prototype switches (shown in the figure as circles). Eight workstations (WS) will be interfaced to the switches as shown, each over 620 Mbps SONET. The control processor (CP), which is remote from the switches, can be connected to one of the switches through a link at either 155 or 620 Mbps. The test bed will also connect to the Project Zeus network through a 620 Mbps SONET link.

For each prototype switch, it is possible to configure any of the input ports as a control port (this is done by means of physical DIP switches that reside on the board). On such ports, a special VPI-VCI combination serves as a dedicated "control" virtual circuit. Control cells (from the control processor) intended for a particular switch must arrive on this dedicated virtual circuit for them to be valid. In addition to these dedicated connections, the CP also sets up dedicated virtual circuits between each workstation and the CP; these are used for exchange of signalling messages between the workstations and the CP.

# 6 CELL FORMATS

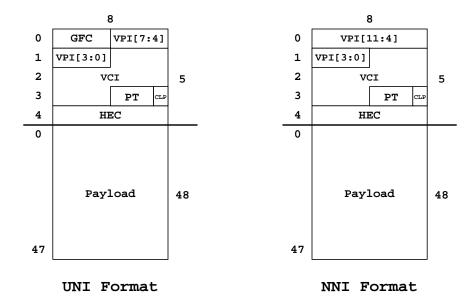

### 6.1 External Data Cell Format

The external data cell format used in the prototype follows the ATM standard. Each ATM cell is 53 bytes long, and carries a 48 byte payload. There are two distinct ATM cell formats: the UNI (User Network Interface) format is used between hosts that are end-points of connections and the first switch encountered in the ATM network; the NNI (Network Network Interface) format is used between pairs of switching nodes within the ATM network. The two interfaces are shown in Figure 13. The only difference between the cell formats for these interfaces is that the first four bits of the

cell form a GFC field in the UNI format, while they are part of the VPI field in the NNI format (i.e., the VPI field is longer by four bits in the NNI format). Referring to Figure 14, the various header fields have the following interpretation (comments that have special relevance to our prototype design have been italicized):

- GFC Generic Flow Control: This 4-bit field is used for carrying local flow control information between an end host and the first ATM switching node to which it is directly connected (it is not carried through end-to-end). This field is ignored in our design.

- VPI Virtual Path Identifier: The ATM standard supports two types of connections (see Figure 15). In virtual path connections, the VCI field is preserved end-to-end, and only the VPI field contents are used by the network to route cells. On the other hand, in virtual circuit connections, both the VCI and the VPI fields are used to route cells, and so neither is preserved end-to-end. Although the NNI cell format supports a 12 bit VPI in the standard, we use only the low-order 8 bits in the prototype.

- VCI Virtual Circuit Identifier: As mentioned earlier, the VCI field is used (along with VPI) for routing cells in a virtual circuit connection. In virtual path connections, it is preserved end-to-end, and can therefore be used by end hosts to demultiplex different cell streams routed on the same virtual path. The ATM standard provides for a 16 bit VCI, but not all VCI values are supported for virtual circuit connections.

- CLP **Cell Loss Priority:** This 1-bit field is used to indicate low priority cells. The source may set this bit to 0 or 1. If the bit is 1, switches along the connection path know that the cell is of low priority, and preferentially discard such cells if the network is encountering congestion.

- PT **Payload Type:** This three bit field, along with some of the other fields in the ATM cell header, determines the cell type. The table in Figure 16 lists the values of various fields and the corresponding cell types. These are as per the ITU recommendation; the ATM forum deviates slightly by making all PT bits and the CLP bit of meta-signalling and general broadcast cells available for use at the ATM layer. The table also lists the action that the prototype switch will take when it receives a cell of each type. For those types that are discarded (except unassigned cells), the switch will set an internal error flag in its maintenance register to remember that such a cell was discarded, and store the header of the most recent one discarded. Unassigned cells are discarded, but no error flag is set, because such cells are likely to be very common under normal operation. A description of each of the defined cell types follows:

- Unassigned cells do not carry any useful data. They characterize available positions, i.e. unused bandwidth, in the cell stream at the ATM layer. These are to be distinguished from IDLE cells, which are used for stuffing unused bandwidth at the physical (PHY) layer, but are not passed to the ATM layer. Unassigned

Cells arrive on the same VCI and VPI, preventing source discrimination without higher level (payload-based) information.

**Figure 15: Virtual Path and Virtual Channel Connections**

C1

А

cells, in contrast, are visible at the ATM layer. The distinction between these two types of cells is made based on the CLP bit; as shown in the table, this bit is 0 for unassigned cells.

- Meta-signalling cells are used for negotiation of which VCI will be used for signalling, and for assignment of other resources used in signalling.

- General broadcast signalling cells carry information that is to be broadcast to all terminals at the UNI.

- **Point-to-point signalling cells** are used to carry signalling messages between two end-points, both of which can either be end-hosts (at the UNI) or switching nodes.

- The **segment and end-to-end** OAM **flow F4 cells** carry operations and maintenance (OAM) information for a particular virtual path, as identified by the VPI field. Notice that the VCI field is used to distinguish these cells from other cells using the same virtual path.

- The **segment and end-to-end** OAM **flow F5 cells** carry OAM information for a particular virtual channel, as identified by the VCI and VPI fields. Notice that the PT bits are used to distinguish these cells from other cells on the same virtual channel.

- **Resource management cells** carry resource management information for a particular virtual path or channel. As yet, the content or use of these cells has not been specified.

• Most cells fall into the category of **user data cells**. The C bit in the PT is used as an indication of congestion in the network. It is initialized to zero by the source, and it gets set to 1 within the network if there is some indication of congestion. Higher layers at the destination can examine the bit and take necessary action (such as sending a source quench packet). The U bit is used at the ATM adaptation layer; in AAL-5, it marks the last cell in an AAL frame.

In the prototype design, meta-signalling, general broadcast, point-to-point signalling, end-to-end F5, and resource management cells are merely propagated unchanged (except for normal VCI translation, as for user data cells) and without interpretation by the switches. Note that normal VCI translation means that such cells may be discarded by the virtual circuit translation table. Unassigned cells are discarded "quietly" (with no error indication) by the receive framer. All F4 cells and segment F5 cells are discarded by the receive framer, and cause an error to be flagged. Cells received that do not match any of the patterns mentioned in Figure 16 are propagated. Finally, and most importantly, we need a special format for the control cells from the remote CP (control processor). User data cells with VPI = 0 and VCI = 32 decimal are used for this purpose.

HEC – Header Error Check: The header error check is an 8 bit CRC that is computed only over the header fields. The CRC computation is based on the polynomial:  $x^8 + x^2 + x + 1$ .

|                                       |                                  | -               |       |     |                                               |  |  |  |  |

|---------------------------------------|----------------------------------|-----------------|-------|-----|-----------------------------------------------|--|--|--|--|

| Cell Type                             | VPI                              | VCI             | РТ    | CLP | Action                                        |  |  |  |  |

| Unassigned Cells                      | 0                                | 0               | ххх   | 0   | discard                                       |  |  |  |  |

| Meta-Signalling Cells                 | 0                                | 1               | 0 X 0 | Y   | propagate                                     |  |  |  |  |

| General Broadcast Cells               | 0                                | 2               | 0 X X | Y   | propagate                                     |  |  |  |  |

| Point-to-point Signalling Cells       | 0                                | 5               | 0 X X | Y   | propagate                                     |  |  |  |  |

| Segment OAM F4 Flow Cells             | X                                | 3               | 0 X 0 | Х   | discard                                       |  |  |  |  |

| End-to-end OAM F4 Flow Cells          | X                                | 4               | 0 X 0 | Х   | discard                                       |  |  |  |  |

| Segment OAM F5 Flow Cells             | X                                | ≠0              | 100   | Х   | discard                                       |  |  |  |  |

| End-to-end OAM F5 Flow Cells          | X                                | ≠0              | 101   | Х   | propagate                                     |  |  |  |  |

| Resource Management Cells             | X                                | ≠0              | 1 1 0 | Х   | propagate                                     |  |  |  |  |

| GBN Switch Control Cells              | 0                                | 32<br>decimal   | ххх   | Х   | propagate if<br>CTRL_EN option<br>pin enabled |  |  |  |  |

| User Data Cells                       | Х                                | > 21<br>decimal | 0 C U | L   | propagate                                     |  |  |  |  |

| any cell not matching a pattern above |                                  |                 |       |     | propagate                                     |  |  |  |  |

|                                       | C. Connection and indication bit |                 |       |     |                                               |  |  |  |  |

C: Congestion experienced indication bit.

U: If this bit is 1, it indicates that this is the last cell of an AAL-5 frame.

- L: Cell Loss Priority bit.

- x: Any value.

- Y: Bit is set to 0 by originating entity, but network may change value.

Figure 16: ATM cell header fields for different cell types, by ITU.

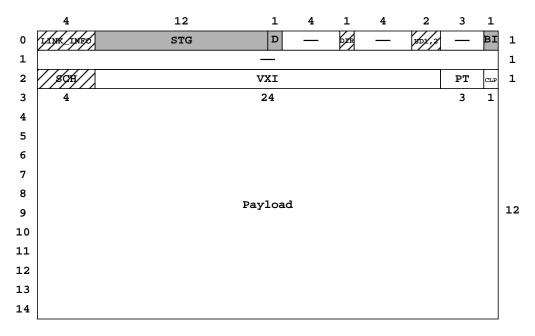

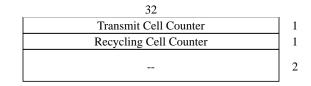

## 6.2 I/O and Recycling Data Cell Format

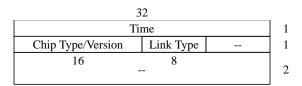

When a data cell enters an IPP, either from the incoming link or recycled from an OPP, it is stored in an intermediate format until it is sent to a switch element. Data cells are also stored in this format in any OPP they go through. This format is shown in Figure 17. All of these fields are explained in Section 6.3.

The STG, D, and BI fields are shaded (see Section 6.3 for a definition of these fields, or any of the other fields in Figure 17). This indicates that they need only be defined for cells that are recycling. These fields are undefined for new data cells that have just arrived on the incoming link, and their values are ignored for data cells leaving on an outgoing link. This format is called the *I/O data cell format* if the STG, D, and BI field values are undefined, or the *recycling data cell format* if they are defined.

The LINK\_INFO, DIR, UD, and SCH fields are marked with diagonal lines (see Section 8.3.1 for a definition of these fields). All of these fields except LINK\_INFO will be filled in for recycled data cells by the OPP chip, but the first version of the IPP chip will ignore these fields. They are only necessary for a planned future version of the IPP chip that supports several reliable multicast features. The LINK\_INFO field will be filled in for link-bound cells by the OPP chip, but the first version of the IPP chip fills them in as four additional bits of the STG field. The second version of the IPP

#### Figure 17: I/O and Recycling Data Cell Format

chip will fill them in with values that are not yet defined. They are optionally passed from the switch to the outgoing link interfaces, so that link interfaces that implement their own priority-based queueing schemes may use them.

In all figures showing cell formats, the bits of values are placed most significant bit to least significant bit, left to right. For fields covering multiple lines in the figure (like the payload in Figure 17, or the time stamp (TS) field in Figure 18), the most significant bits are placed in the top line, continuing down to the least significant bits in the bottom line.

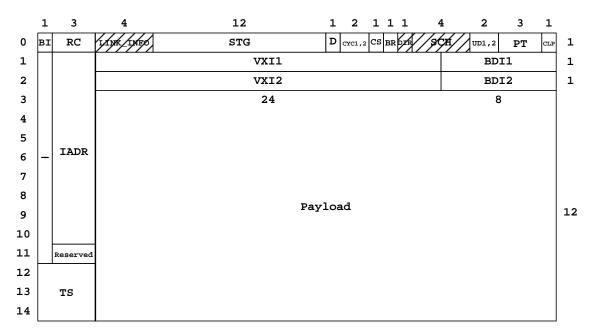

### 6.3 Internal Data Cell Format

When a data cell enters the IPP, many of its fields get interpreted, and a VXT table lookup yields output port numbers to which the cell will be forwarded (either for output or for being recycled). This and some other information, along with the cell payload itself, are then encapsulated by the IPP in a new type of cell, the format for which is shown in Figure 18. This cell format is called the internal data cell format. Note that the format has fifteen 36-bit words. It is sent to the four parallel switch planes in 16 clock ticks. The extra tick is desirable for several reasons: it allows a little more time for the switch elements to complete their tasks, it leaves a guard time between cell times, and it makes the cell time equal to 4 times 4 clock ticks, which is useful in the port processors because the cell store memories can be accessed 4 times per cell time, each time using 4 clock ticks (see Section 8.2). The first four bit-columns of the cell contain control information that is used by the switch elements to route the cell through the fabric; these are called control columns. The remaining 32 bit-columns contain, in addition to the original cell payload, control information that needs to be interpreted only by the port processors. All four of the switching planes need to have access to the four control columns, so they are forwarded by the IPP to all four planes. The remaining 32 bit-columns are divided up, eight per plane. Hence, each switching plane receives data on 12 pins per port. All four switching planes are designed to behave identically (since they all receive the same four control columns), so the switching of the cell through the four planes is fully synchronous, and the cell emerges from the switch fabric (possibly after having been copied to multiple output ports) and is received by the OPP in precisely the same format as it entered, and over a period of 16 clock ticks. Once it enters the OPP, it gets converted back to the I/O or recycling data cell format. The various fields in the internal data cell format have the following interpretation:

- BI Busy/Idle cell: This 1-bit field is used to distinguish between idle cell slots and busy (i.e., data or control) cell slots. It is 0 for an idle cell slot and 1 for a busy cell slot.

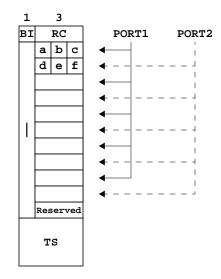

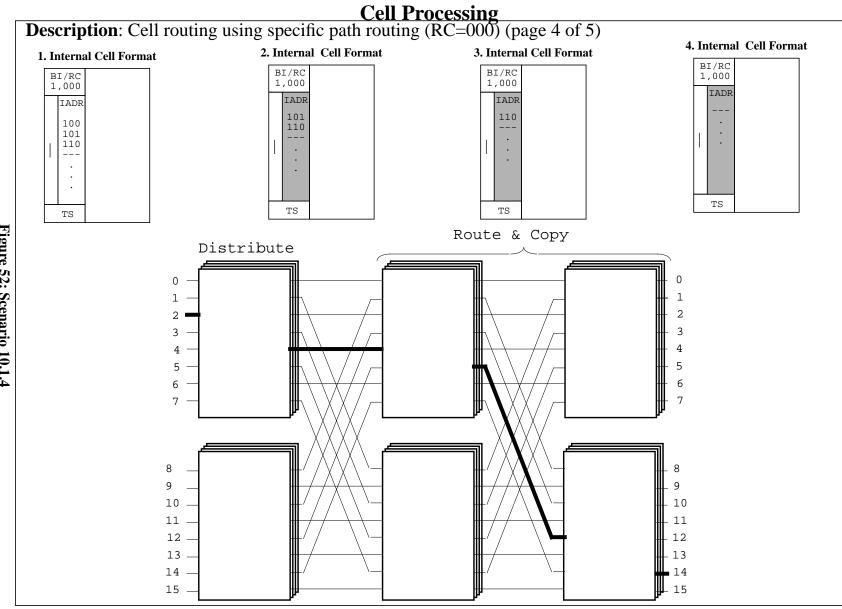

- RC Routing Control: When these three bits are all 0 (i.e., RC = 000), then the IADR field (see below) precisely enu-

#### **Figure 18: Internal Data Cell Format**

merates a specific path through the switching fabric. In all other cases, the IADR field specifies two output port numbers, and the RC bits are used to determine whether the cell should be routed to only one of these ports, or to both, or to the entire range of output port numbers falling in between (and including) the two ports. If we call the first port number in the IADR field PORT1, and the second one PORT2, then the three RC bits have the following encodings:

| RC = 000 | Specific path through switching fabric.                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RC = 010 | Route cell only to output port number PORT1.                                                                                                 |

| RC = 001 | Route cell only to output port number PORT2.                                                                                                 |

| RC = 011 | Route cell to the two output port numbers PORT1 and PORT2.                                                                                   |

| RC = 111 | Route cell to all port numbers falling in the range from PORT1 up to PORT2, inclu-<br>sive. Note: PORT1 must be less than or equal to PORT2. |

Note that when the multipoint connection tree (see Figure 3) is a full binary tree, the RC field has a value of 011. When we have a point-to-point connection, or if one of the internal nodes of the multipoint connection tree has only one child, the RC field may take on the value 010 or 001. The last entry in the above table (RC = 111) has been provided to allow the construction of multicast connection trees with larger branching factors, reducing the required speed advantage and the delay due to recycling. The reason for the restriction that PORT1 must be less than or equal to PORT2 is that it makes the specification and implementation of this feature in the SE chips simpler. There is no restriction on the relative values of PORT1 and PORT2 for cells with other RC values. They may be equal, and in the case of RC=011 cells, this causes two copies of the cell to appear at the same output port, one at a time. They can be distinguished because one copy has RC=010 when arriving at the OPP chip, and the other has RC=001.

D – Data Cell: This 1-bit field is used to distinguish between data and control cells. It is 1 for a data cell, and 0 for a control cell.

CYC1,CYC2 - Recycle Cell: These two bits are used to identify which copies of the cells will be recycled. If RC is 010

or 011, then CYC1 controls whether the copy sent to output port processor number PORT1 is recycled or sent to the outgoing link attached to the OPP (1=recycle, 0=send out on the link). If RC is 001 or 011, then CYC2 controls whether the copy sent to output port processor number PORT2 is recycled or sent to the outgoing link. If RC is 000, then CYC1 controls whether the single copy is recycled. If RC is 111, then CYC1 controls whether all copies are recycled (there is no way for some to recycle, and some not to recycle).

- CS Continuous Stream: At connection setup time, end-applications specify whether the cell stream on the virtual circuit contains continuous or discrete media. Continuous media connections are those in which the data rate is either constant, or has low variance over time (e.g., many video and voice encodings). Discrete media connections have higher variance in their data rates, and are often described as "bursty". The type of connection is recorded by the CP in the VXT tables in appropriate IPPs. When a cell gets translated by an IPP to the internal format, the CS bit field gets a value of 1 if the connection carries continuous media traffic, and 0 if it carries discrete media. Further down the line, an OPP will use this information to direct traffic into one of two FIFO buffers. The real-time requirements of continuous stream data then dictate that cells in the continuous stream buffer get priority over cells in the discrete stream buffer. Moreover, since continuous media traffic is typically non-bursty, we can afford to make the continuous stream buffer much smaller than its discrete counterpart. Further details can be found in Section 8.2.8 and Section 8.3.6.

- BR **Bypass Resequencer:** When this bit is 0, the cell is time stamped and resequenced normally, as described in Section 3.2, Section 3.3, and Section 8.3.2. When this bit is 1, the cell is time stamped normally, but the resequencer ignores the time stamp and always assigns the cell an age equal to the age threshold of the resequencer. In the absence of other cells already in the resequencer with the same age, such cells will leave the resequencer within one cell time. This feature is intended to provide the minimum propagation delay through the entire switch that can be achieved. It may be useful if the receiver does not require cells to arrive in the same order that they were sent. The switch can still guarantee that the cells will arrive in the order sent, for connections with BR=1, if all cells follow the same path through the switching fabric, and if the interval between consecutive cells in the connection. The second requirement can easily be met by choosing to use RC=000 for all cells in the connection. The second requirement occurs because the current implementation of the switch element chips can misorder two cells in the same connection if they arrive within 8 cell times of each other. The sequence of the cells is guaranteed to be correct if every cell arrives at least 8 cell times after the previous cell in the connection.

- IADR **Internal Address:** If RC is 000, then this 30-bit field specifies a fixed path through the switching network. As the cell is guided along this specific path, each successive switching element uses the first three bits of the IADR field to select one of its 8 output ports, and then discards these three bits and shifts the remaining bits up by one row (so that the downstream switch element can again use the first three bits to select an output port). When RC is not 000, the IADR field contains two "nibble" interleaved output port numbers, which have been referred to earlier as PORT1 and PORT2. See the description of the RC field above for the interpretation and use of these two port identifiers. Here a "nibble" means a group of 3 bits. For details on the exact placement of bits in this field, see the description of the EADR field in Section 6.4 and the conversion of the EADR field to the IADR field in Section 8.2.10.

- TS **Timestamp:** This field is used to indicate to the OPP the time at which the cell entered the switch fabric, and it is filled in by the IPP just before the cell enters the switch fabric. Recall that the OPP needs this information for doing resequencing (see Sections 3.2 and 3.3). Under normal circumstances, the high-order 11 bits of the TS are derived from the local cell clock, and the lowest order bit is zero. When transitional time stamping is turned on, the time stamp is set to a value larger than the current time, and the lowest order bit corresponds to the *half-step bit* that is used to prevent the cell resequencer from misordering cells when one of the internal nodes in a connection tree is dropped (see Section 3.3). See Section 8.2.10 for more implementation details on transitional time stamping.

- STG Source Trunk Group: The source trunk group field contains the 12-bit trunk group identifier of the IPP where the cell first arrived from an external link. To understand the need for this field, we need to look at the way multipoint-to-multipoint connections would be handled (these connections have the property that there could be multiple endpoints sending into the connection, and each endpoint receives cells sent by every other endpoint on the connection). Figure 19 shows a connection tree for such a connection. When two or more of the

Figure 19: Connection Tree for Multipoint-to-Multipoint Connection

endpoints belonging to the connection interface to ports on the same switch, cells from all of these ports are first sent to a common distribution port (corresponding to an internal node in the connection tree). From there, the routing and copying proceeds normally to all the endpoints in the connection. However, it is often necessary that the source of a particular cell does not receive a copy of that cell; it should only receive copies of cells from other endpoints. A simple way to enforce this is to let the OPP discard a cell if it is found to have originated from the same port (i.e., the IPP and the OPP have the same port number). The OPP has no way of knowing where the cell originated unless this information is encapsulated within the cell itself; this explains the need for the STG field. When the UD bit (see below) is set, a cell arriving at an OPP whose trunk group identifier matches the STG field is discarded. See Section 10.2.5 for a discussion about why these numbers are called "trunk group identifiers" instead of "port identifiers".

- UD1,UD2 Upstream Discard: If the appropriate one of these two bits is set, a copy of the cell will not be sent to the originating endpoint in a multipoint-to-multipoint connection (see the discussion of the STG field above for more details). It would be a good idea for the CP to set the upstream discard bits for all connections (multipoint or point-to-point) except those in which "echo" cells are explicitly requested. Although the name "upstream discard" is perhaps too well entrenched in the documentation, VHDL code for the chips, and source code for the control software, it might help to think of this field with the more descriptive name "suppress echo".

- PT Payload Type: This field contains a copy of the PT field from the original ATM cell.

- CLP **Cell Loss Priority:** This bit is a copy of the CLP bit value from the original ATM cell. It may be set by an IPP if the VXT table entry for the virtual path/channel on which the cell arrives has its Set CLP (SC) bit equal to 1 (refer to Section 7.1 for a description of the SC bit).

- VXI1, VXI2 Virtual Path/Circuit Identifier: Each of these fields is three bytes in length; the first byte is the eight least significant bits of a VPI, and the next two bytes contain a VCI. If RC is 000, 010, or 111 when the cell reaches an OPP, the OPP uses the contents of the VXI1 field to fill in the VXI field in the I/O or recycling data cell format (Figure 17), as appropriate. If RC is 001, the VXI2 field is used instead. The OPP's should never receive a cell with RC=011 (i.e., this would be a sign of a malfunctioning switch element chip, or some other hardware fault). If the cell is to be recycled, this VXI value is used by the IPP to perform a VXT lookup on the cell. If the cell is to be sent out on the link, this VXI value is placed in the header of the outgoing ATM cell.

- BDI1, BDI2 **Block Discard Index:** These fields can be other than 0 only when the connection to which the cell belongs is using AAL 5 at the adaptation layer. In AAL 5, a large transport level frame is split into a number of 48 byte chunks that are used to fill in the ATM cell payload before transmission. The last cell containing data from the frame may contain fewer than 48 bytes of real data, and it is marked by setting the U bit in the PT field of the cell (see Figure 16). Typically, if even one cell in an AAL 5 frame is lost or corrupted, the entire frame would be discarded (and possibly retransmitted). Hence, if the switch finds it necessary to discard a cell belonging to an AAL-5 frame, it can optimize by discarding all remaining cells within that frame except the last one. Since a cell would be discarded during times of congestion, discarding all of these cells may help reduce the

congestion further. See Section 8.3.5 for more details on the exact congestion control method used. The BDI field, when not 0, contains a tag that is used to differentiate connections using this feature. Since the field is 8 bits long, it follows that we can have no more than 255 such connections. Note that it is the job of the CP to assign a non-zero BDI for some connections. If RC is 000, 010, or 111 when the cell reaches an OPP, the OPP uses BDI1 as the BDI value for the cell. If RC is 001, then BDI2 is used instead.

Payload: The payload from the original ATM cell gets carried over into this field in the internal format.

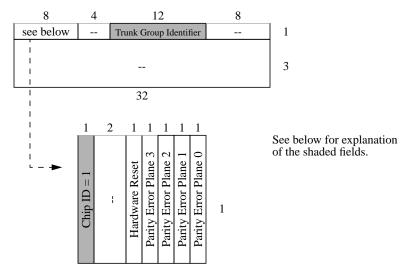

**Parity:** Although it has not been shown in the figure, one horizontal parity bit is generated by the IPP for each of the four switching planes. The parity is odd, and it is computed horizontally, i.e., one parity bit is generated for every 12 bits (4 control + 8 data) passed to a switch element. Thus, in one clock tick, the IPP would need to generate 4 parity bits in all. See Section 9.6 for further details.

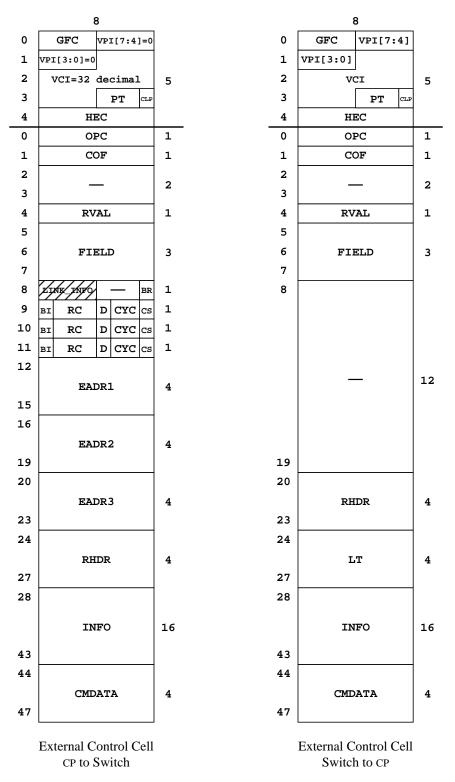

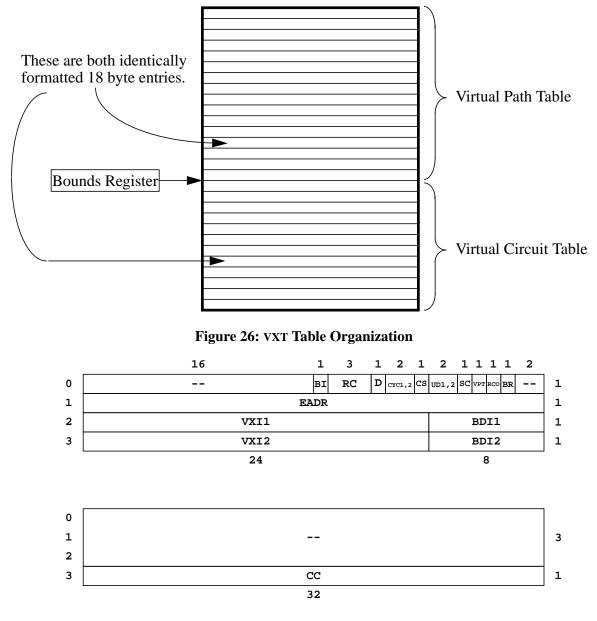

## 6.4 Control Cell Format

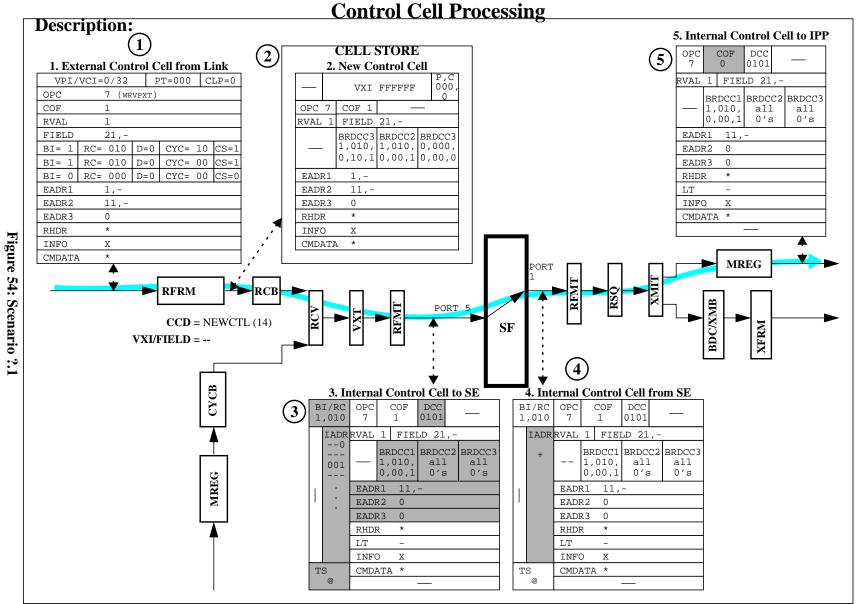

Control cells from the remote CP arrive at the appropriately configured input port of a switch on a virtual circuit with VPI = 0 and VCI = 32 decimal. It is not yet certain whether the ATM interface hardware in the CP will allow us to send such cells, so the method that the switch uses to recognize control cells may change. However, the rest of this section is written under the assumption that cells with VPI = 0 and VCI = 32 may be sent.

If the CP is attached by a direct link to a switch it is controlling, then the CP sends a cell with VPI/VCI equal to 0/32. If the CP controls a switch to which it has no direct link, then it creates a connection through an intermediate switch to the desired switch. If the intermediate switch is also a Washington University gigabit switch, then this connection has a VPI/VCI other than 0/32, so the intermediate switch propagates the cells as normal data cells. In general, there could be several intermediate switches in a path to the switch at which the control cell will perform its operation. The last such intermediate switch is set up by the CP to translate the incoming cells to VPI=0, VCI=32 on the link to the desired switch. Thus, only the last switch on the path interprets the cell as a control cell.

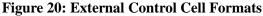

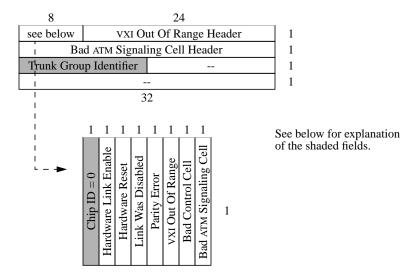

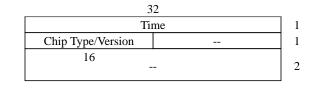

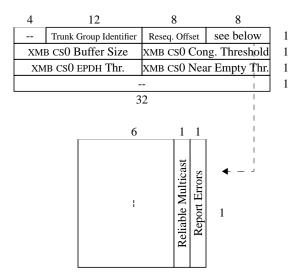

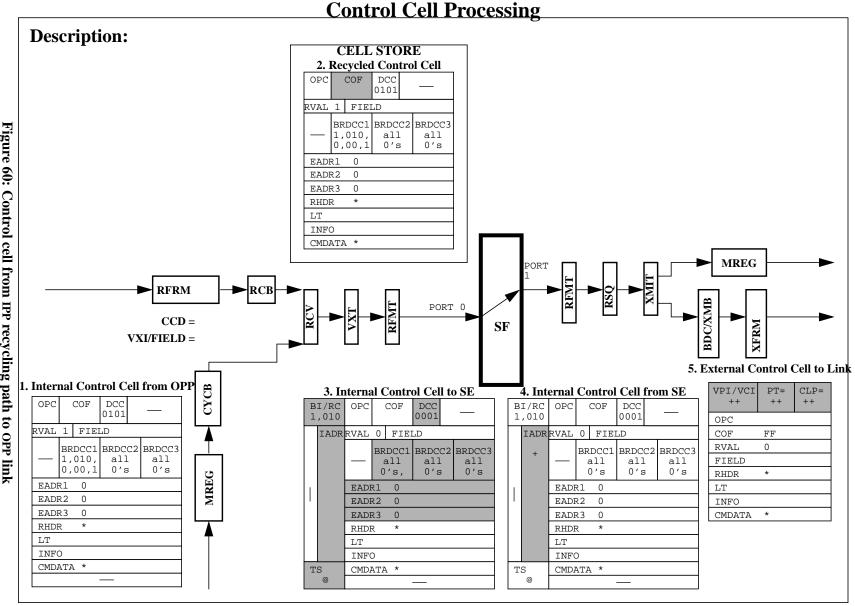

The cell format as interpreted by an IPP on the target switch is illustrated in the left part of Figure 20. Once the actions specified in the control cell have been performed, the results (if any) are encapsulated in a similar control cell, shown in the right part of Figure 20, by the appropriate OPP and returned to the CP. The RHDR field in a CP to switch control cell is used to fill in the ATM cell header of the corresponding switch to CP control cell. In this way, the CP can ensure that the returning control cell gets routed correctly.

When an external control cell enters an IPP, it gets converted to a 36-bit format analogous to the internal data cell format. This format is shown in Figure 21. Notice that the four control columns carry information in the same format as the corresponding columns of an internal data cell. The D, CYC1, CYC2, CS, and BR fields are also in the same positions as in the internal data cell format. As before, the internal cell format gets converted to the corresponding external format in the OPP before being sent out on the link.

A description of the various fields in the control cell formats (both internal and external) follows. Fields that have already been described either as part of the ATM cell header format, or as part of the internal data cell format, are not described again. Throughout the rest of this section, we refer to control cells from the CP to the switch as incoming control cells, and those from the switch to the CP as outgoing control cells.

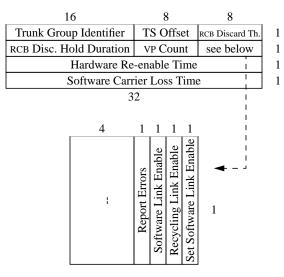

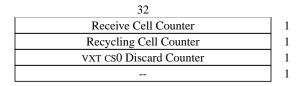

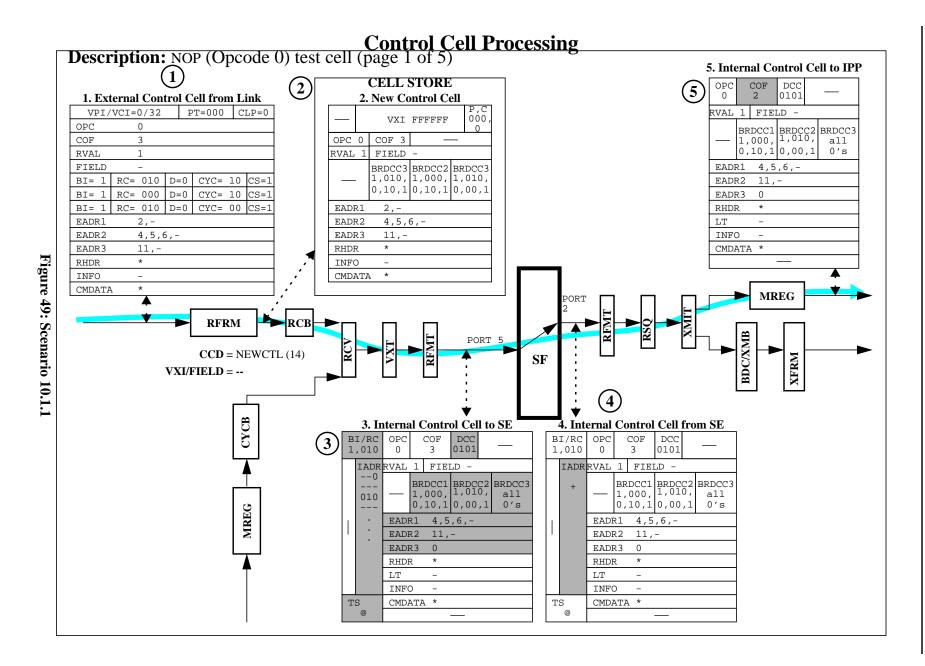

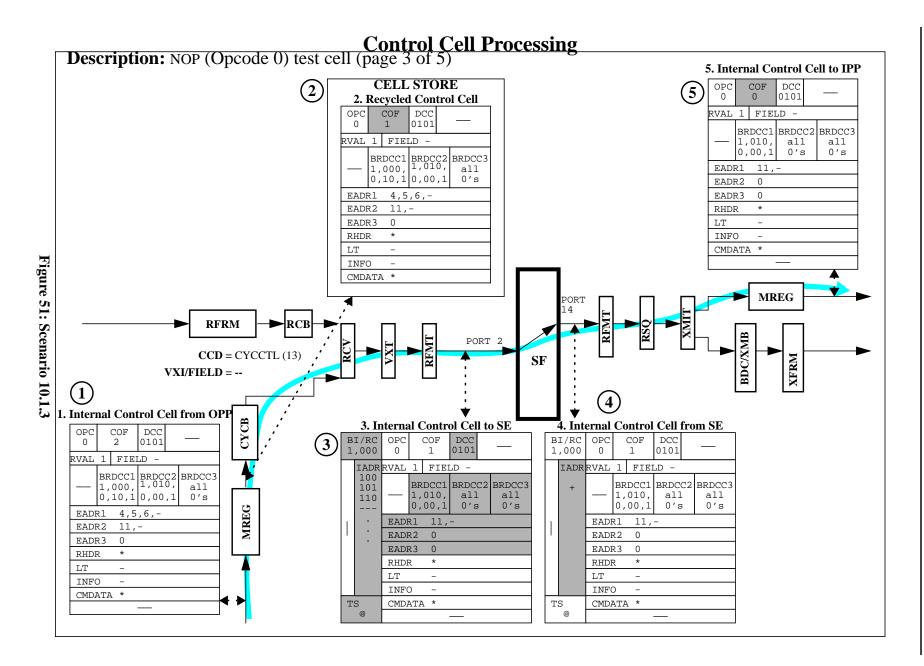

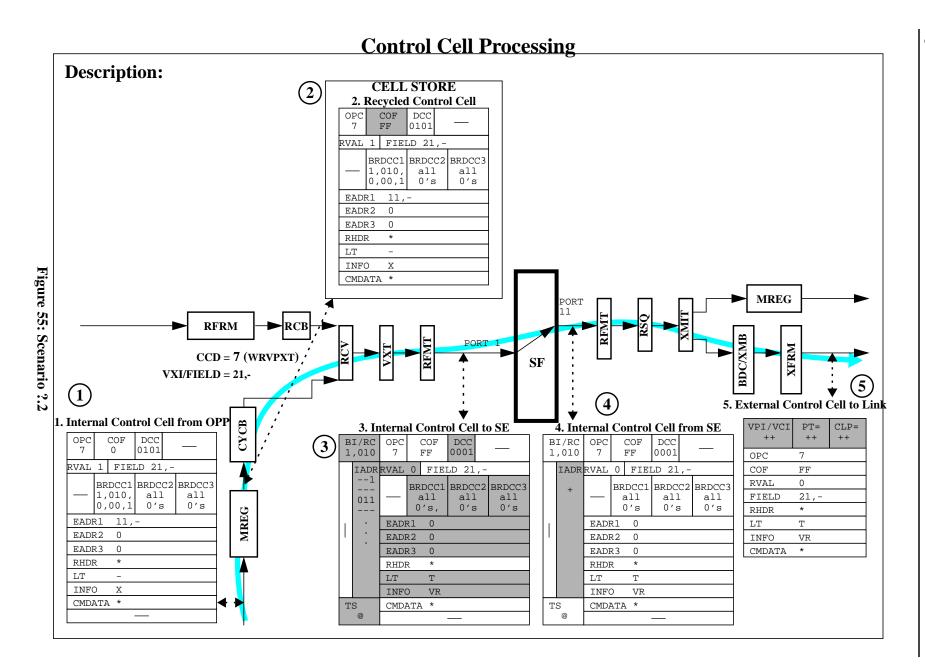

OPC – **Operation Code:** On an incoming control cell, the opcode is a command to the target port processor (the COF field is used to address a particular port processor, see below). Each port processor chip contains a number of status and command registers that can be read from or written to; these jointly comprise what is called the *maintenance register*. Each port processor also contains a VXT (virtual circuit translation table), as well as a number of error flags. The command specified by the opcode can be used to initiate a hardware reset of all chips comprising the switch, clear all error flags in all chips, or read or modify maintenance register fields or VXT table entries. The various opcodes that have been defined are listed in Figure 22. The mnemonics in the second column of the table will henceforth be used to identify the opcode specified in a control cell. Subsequent sections of the document elucidate the semantics of each of these opcodes.

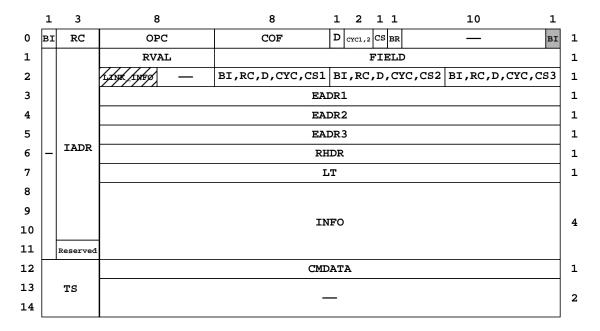

EADR1, EADR2, EADR3 - **External Routing Addresses:** Most control cell operations require access to the maintenance register or a VXT entry in one of the port processors. As can be seen in Figure 23(a), it is possible for a control cell to reach any port processor chip by recycling it at least once. However, if the CP needs to test a particular

**Figure 21: Internal Control Cell Format**

(a) Accessing IPP #3 or OPP #3.

(b) Routing from IPP #3 to OPP #6.

### Figure 23: Routing a Control Cell

path through the switch fabric, we must be able to make the cell pass through an IPP of our choice, and then get routed to an OPP of our choice. As can be seen from Figure 23(b), we can do this in the general case if control cells can be recycled at least twice (in other words, it can traverse the switch fabric at least three times). Note that once we can make a control cell move from a specific IPP to a specific OPP, we can select the exact path through the switching fabric, by setting the RC field to 000 (see Section 6.3), and the IADR field to the appropriate value.

| Opcode   | Command  | Description                                                                                                                                                                                                       |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | NOP      | No operation (used for cells that test switch operation and internal paths)                                                                                                                                       |

| F0 (hex) | RST      | Hard reset of all chips. The opcode is F0 instead of 1 so that a single bit error in a NOP control cell does not transform it into a RST.                                                                         |

| 2        | CLRERR   | Clear all error flags in all chips                                                                                                                                                                                |

| 3        | RDVPXT   | Read virtual path table entry from VXT (everything except CC field)                                                                                                                                               |

| 4        | RDVCXT   | Read virtual circuit table entry from VXT (everything except CC field)                                                                                                                                            |

| 5        | RDVPXTCC | Read cell counter (CC) from virtual path table                                                                                                                                                                    |

| 6        | RDVCXTCC | Read cell counter (CC) from virtual circuit table                                                                                                                                                                 |

| 7        | WRVPXT   | Write virtual path table entry into VXT (does not write CC field)                                                                                                                                                 |

| 8        | WRVCXT   | Write virtual circuit table entry into VXT (does not write CC field)                                                                                                                                              |

| 9        | WRVPXTTR | Write virtual path table entry into VXT and start transitional time stamping                                                                                                                                      |

| 10       | WRVCXTTR | Write virtual circuit table entry into VXT and start transitional time stamping                                                                                                                                   |

| 11       | WRVPXTCC | Write cell counter (CC) to virtual path table (for testing only)                                                                                                                                                  |

| 12       | WRVCXTCC | Write cell counter (CC) to virtual circuit table (for testing only)                                                                                                                                               |

| 13       | ERRORS   | Return a cell only if error conditions exist (due to a mistake in the IPP and OPP chip implementations, such cells should have FIELD=0, or else the fields read and returned may not be the desired error flags). |

| 14       | RDMR     | Read maintenance register field                                                                                                                                                                                   |

| 15       | WRMR     | Write maintenance register field                                                                                                                                                                                  |

#### Figure 22: Control Cell Opcodes

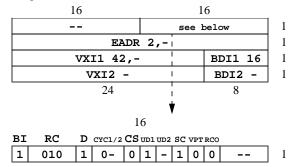

To allow for three traversals through the switch fabric, the control cell format has three sets of the six fields BI, RC, D, CYC, CS, and EADR (note that CYC here refers to a 2 bit value that is CYC1 followed by CYC2). Each of these fields has a numeric index that identifies the set to which it belongs. The set of fields with index 1 are used to fill in the corresponding fields in the internal control cell format during the first pass through the switch; on the second pass (if any), the fields with index 2 are used, and on the third pass (if any), the fields with index 3 are used. The BR bit used in the first row of the internal control cell format is always copied from the BR bit of the CP to switch external control cell format. Since the RC and IADR fields in the four control columns are precisely those used by the switching fabric to route cells, the CP has the capability of choosing a precise route through the fabric for its control cells.

The format of the EADR fields in the external control cell format is shown in Figure 24. In this figure, each box represents one bit, bit 31 is the most significant bit, and bit 0 is the least significant bit. The fields are 32 bits long, but bits 16 and 0 are ignored by the switch. If there are two port numbers to specify (i.e., this cell is not to be routed on a specific path), then the first port number should be placed in the most significant half of the 32 bits, and the second port number should be placed in the least significant half. No matter how many bits it takes to specify a port number, the first one should be placed in the EADR field as far left as possible, subject to the restriction that its last (i.e., least significant) bit is in one of the following bit positions: 29, 26,

| port1 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| PORT2 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | ß  |

**Figure 24: EADR Field Format**

23, 20, 17. The second port number should be placed in the corresponding position in the second half of the field, i.e., such that its last bit position is one of: 13, 10, 7, 4, 1. For example, for a switch with 8 ports, port numbers contain 3 bits each. The first port number should be placed in bits 31..29, and the second should be placed in bits 15..13. For a switch with 32 ports, port numbers contain 5 bits each. The first port number should be placed in bits 14..10. All other bits are ignored by the switch.

If the EADR field is used to specify a specific path through the switch, then it contains a sequence of three bit switch element output port numbers. The first number is in bits 31..29, but the second is in bits 15..13. The third is in bits 28..26, and the fourth is in bits 12..10, etc. Each odd numbered port number is in the next three bits of the most significant half of the field, and the immediately following even numbered port number is in the corresponding position in the least significant half of the field. For example, for a switch with 8 ports, only a single switch element output port number is needed, and it is stored in bits 31..29. For a 32 port switch, there are three stages of switch elements, so three switch element output port numbers are needed. The first is in bits 31..29, the second is in bits 15..13, and the third is in bits 28..26. All other bits of the EADR field are ignored by the switch.

The formats for the two port and specific path EADR fields were chosen to make the hardware that converts the EADR field to the IADR field (in the IPP chips, see Section 8.2.10), and the hardware that interprets the IADR field (in the switch element chips), simple.

- RHDR **Return Header:** The return header field is 4 bytes long, and it contains the ATM cell header that is to be used in a control cell returning to the CP (except for the HEC, which is generated by the OPP). As was mentioned earlier, this feature enables the CP to ensure that a returning control cell is correctly routed to its destination (the CP).

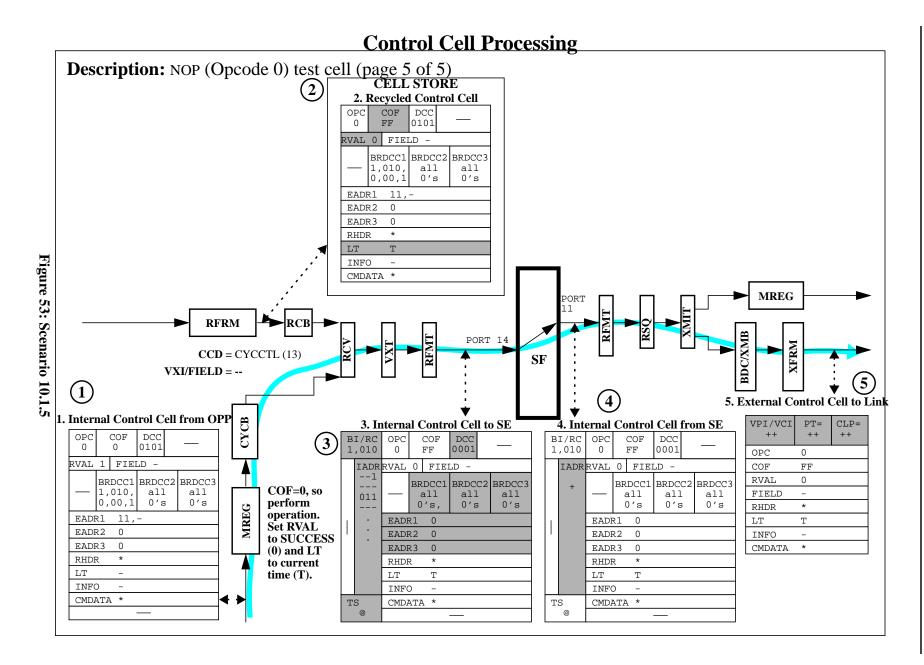

- COF **Control Offset:** Although the three EADR fields (along with other fields comprising the three sets described earlier) permit the CP to select which port processors a control cell will visit, these fields by themselves cannot be used to isolate the point at which the control operation is performed. The COF field overcomes this deficiency. A control cell that performs a reset (RST) or clear error (CLRERR) operation is interpreted by the first IPP chip that it reaches, regardless of the COF value. For all other operation codes, however, every OPP chip that the control cell recycles out of, and every IPP chip that the control cell recycles into, may interpret the control cell. Control cells cannot be interpreted when newly arrived on a link to an IPP, or when leaving on a link from an OPP.

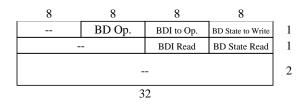

At every point along the path visited by a control cell where it may be interpreted, the COF field is examined. If COF=0, the operation is performed, otherwise the component simply propagates the cell without performing any operation. In any case, the value in the COF field is decremented before propagating the cell.